174 AMD Geode™ SC3200 Processor Data Book

Core Logic Module - Register Summary

32581C

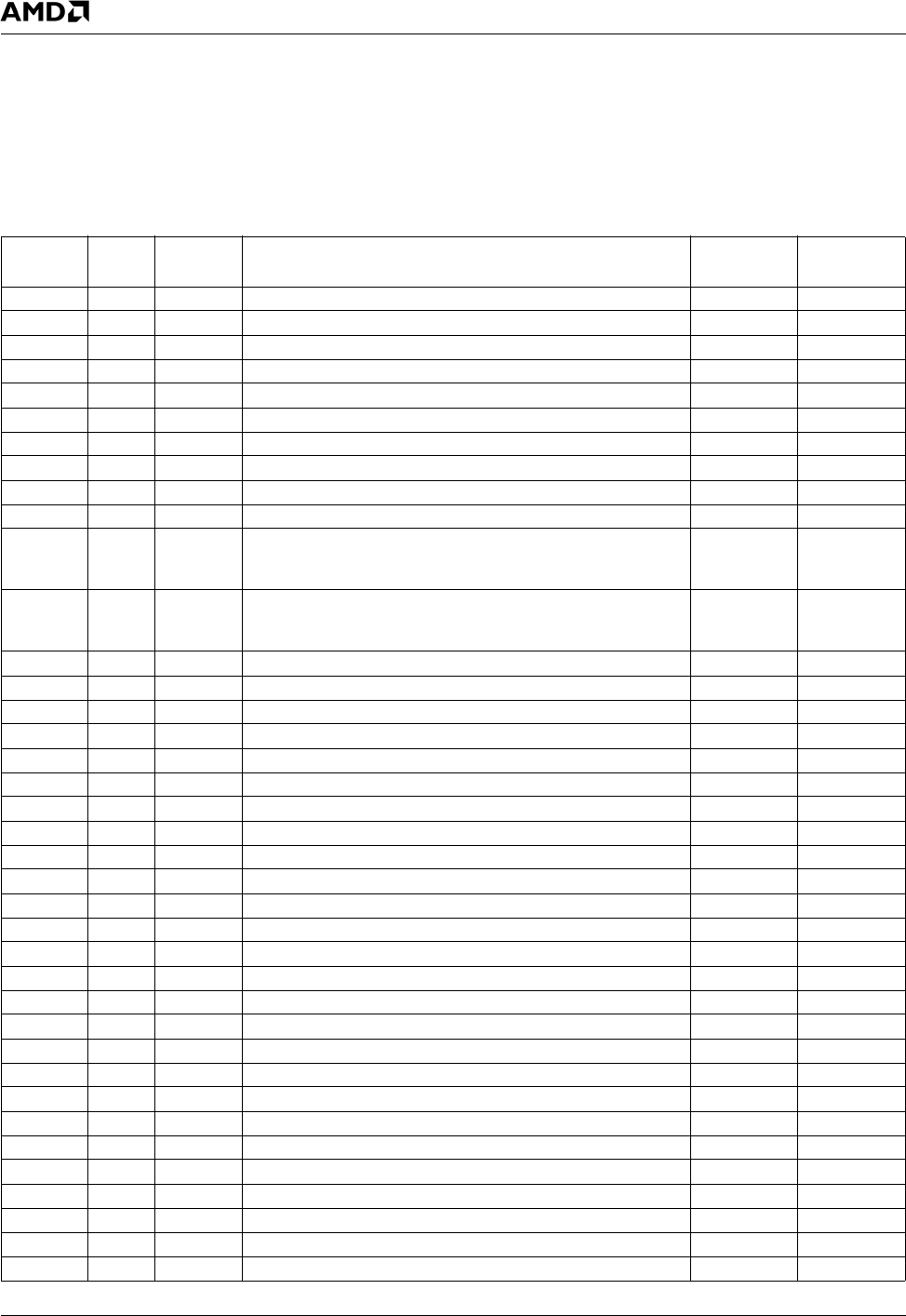

6.3.2 Register Summary

The tables in this subsection summarize the registers of

the Core Logic module. Included in the tables are the regis-

ter’s reset values and page references where the bit for-

mats are found.

Note: Function 4 (F4) is for Video Processor support

(although accessed through the Core Logic PCI

configuration registers). Refer to Section 7.3.1

"Register Summary" on page 327 for details.

Table 6-14. F0: PCI Header/Bridge Configuration Registers

for GPIO and LPC Support Summary

F0 Index

Width

(Bits) Type Name

Reset

Value

Reference

(Table 6-29)

00h-01h 16 RO Vendor Identification Register 100Bh Page 188

02h-03h 16 RO Device Identification Register 0500h Page 188

04h-05h 16 R/W PCI Command Register 000Fh Page 188

06h-07h 16 R/W PCI Status Register 0280h Page 189

08h 8 RO Device Revision ID Register 00h Page 190

09h-0Bh 24 RO PCI Class Code Register 060100h Page 190

0Ch 8 R/W PCI Cache Line Size Register 00h Page 190

0Dh 8 R/W PCI Latency Timer Register 00h Page 190

0Eh 8 RO PCI Header Type Register 80h Page 190

0Fh 8 RO PCI BIST Register 00h Page 190

10h-13h 32 R/W Base Address Register 0 (F0BAR0) — Sets the base address for

the I/O mapped GPIO Runtime and Configuration Registers (sum-

marized in Table 6-15).

00000001h Page 190

14h-17h 32 R/W Base Address Register 1 (F0BAR1) — Sets the base address for

the I/O mapped LPC Configuration Registers (summarized in

Table 6-16)

00000001h Page 190

18h-2Bh --- --- Reserved 00h Page 190

2Ch-2Dh 16 RO Subsystem Vendor ID 100Bh Page 190

2Eh-2Fh 16 RO Subsystem ID 0500h Page 190

30h-3Fh --- --- Reserved 00h Page 190

40h 8 R/W PCI Function Control Register 1 39h Page 191

41h 8 R/W PCI Function Control Register 2 00h Page 191

42h --- --- Reserved 00h Page 192

43h 8 R/W PIT Delayed Transactions Register 02h Page 192

44h 8 R/W Reset Control Register 01h Page 192

45h --- --- Reserved 00h Page 193

46h 8 R/W PCI Functions Enable Register FEh Page 193

47h 8 R/W Miscellaneous Enable Register 00h Page 193

48h-4Bh --- --- Reserved 00h Page 193

4Ch-4Fh 32 R/W Top of System Memory FFFFFFFFh Page 194

50h 8 R/W PIT Control/ISA CLK Divider 7Bh Page 194

51h 8 R/W ISA I/O Recovery Control Register 40h Page 194

52h 8 R/W ROM/AT Logic Control Register 98h Page 195

53h 8 R/W Alternate CPU Support Register 00h Page 195

54h-59h --- --- Reserved 00h Page 196

5Ah 8 R/W Decode Control Register 1 01h Page 196

5Bh 8 R/W Decode Control Register 2 20h Page 196

5Ch 8 R/W PCI Interrupt Steering Register 1 00h Page 197

5Dh 8 R/W PCI Interrupt Steering Register 2 00h Page 197

5Eh-5Fh --- --- Reserved 00h Page 197

60h-63h 32 R/W ACPI Control Register 00000000h Page 198

64h-6Bh --- --- Reserved 00h Page 198