AMD Geode™ SC3200 Processor Data Book 259

Core Logic Module - IDE Controller Registers - Function 2

32581C

6.4.3.1 IDE Controller Support Registers

F2 Index 20h, Base Address Register 4 (F2BAR4), points

to the base address of where the registers for IDE control-

ler configuration are located. Table 6-36 gives the bit for-

mats of the I/O mapped IDE Controller Configuration

registers that are accessed through F2BAR4.

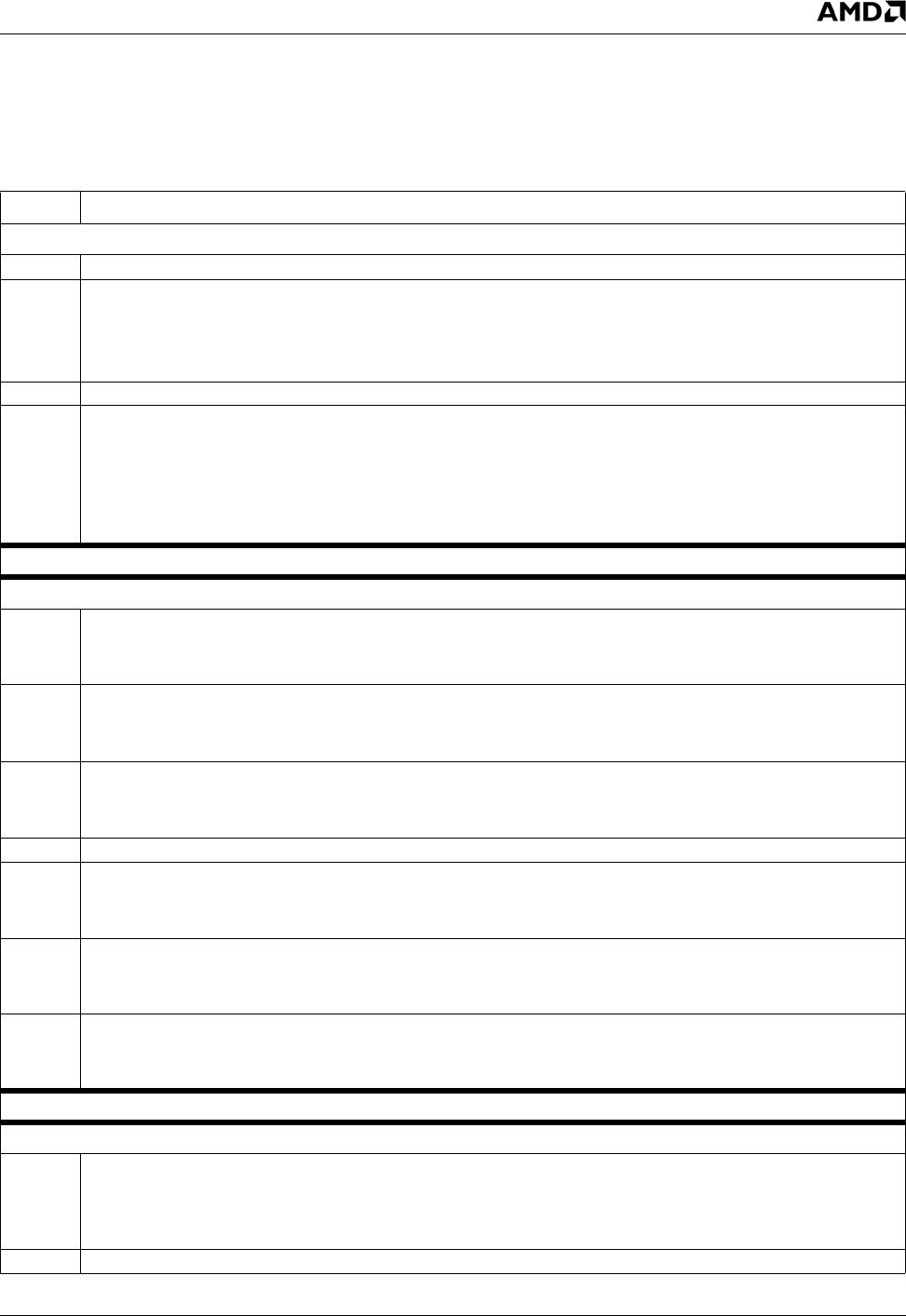

Table 6-36. F2BAR4+I/O Offset: IDE Controller Configuration Registers

Bit Description

Offset 00h IDE Bus Master 0 Command Register — Primary (R/W) Reset Value: 00h

7:4 Reserved. Must be set to 0. Must return 0 on reads.

3 Read or Write Control. Sets the direction of bus master transfers.

0: PCI reads performed.

1: PCI writes performed.

This bit should not be changed when the bus master is active.

2:1 Reserved. Must be set to 0. Must return 0 on reads.

0 Bus Master Control. Controls the state of the bus master.

0: Disable master.

1: Enable master.

Bus master operations can be halted by setting this bit to 0. Once an operation has been halted, it cannot be resumed. If this

bit is set to 0 while a bus master operation is active, the command is aborted and the data transferred from the drive is dis-

carded. This bit should be reset after completion of data transfer.

Offset 01h Not Used

Offset 02h IDE Bus Master 0 Status Register — Primary (R/W) Reset Value: 00h

7 Simplex Mode. (Read Only) Indicates if both the primary and secondary channel operate independently.

0: Yes.

1: No (simplex mode).

6 Drive 1 DMA Enable. When asserted, allows Drive 1 to perform DMA transfers.

0: Disable.

1: Enable.

5 Drive 0 DMA Enable. When asserted, allows Drive 0 to perform DMA transfers.

0: Disable.

1: Enable.

4:3 Reserved. Must be set to 0. Must return 0 on reads.

2 Bus Master Interrupt. Indicates if the bus master detected an interrupt.

0: No.

1: Yes. Write 1 to clear.

1 Bus Master Error. Indicates if the bus master detected an error during data transfer.

0: No.

1: Yes. Write 1 to clear.

0 Bus Master Active. Indicates if the bus master is active.

0: No.

1: Yes.

Offset 03h Not Used

Offset 04h-07h IDE Bus Master 0 PRD Table Address — Primary (R/W) Reset Value: 00000000h

31:2 Pointer to the Physical Region Descriptor Table. This bit field contains a PRD table pointer for IDE Bus Master 0.

When written, this field points to the first entry in a PRD table. Once IDE Bus Master 0 is enabled (Command Register bit 0

= 1), it loads the pointer and updates this field (by adding 08h) so that is points to the next PRD.

When read, this register points to the next PRD.

1:0 Reserved. Must be set to 0.