70 AMD Geode™ SC3200 Processor Data Book

General Configuration Block

32581C

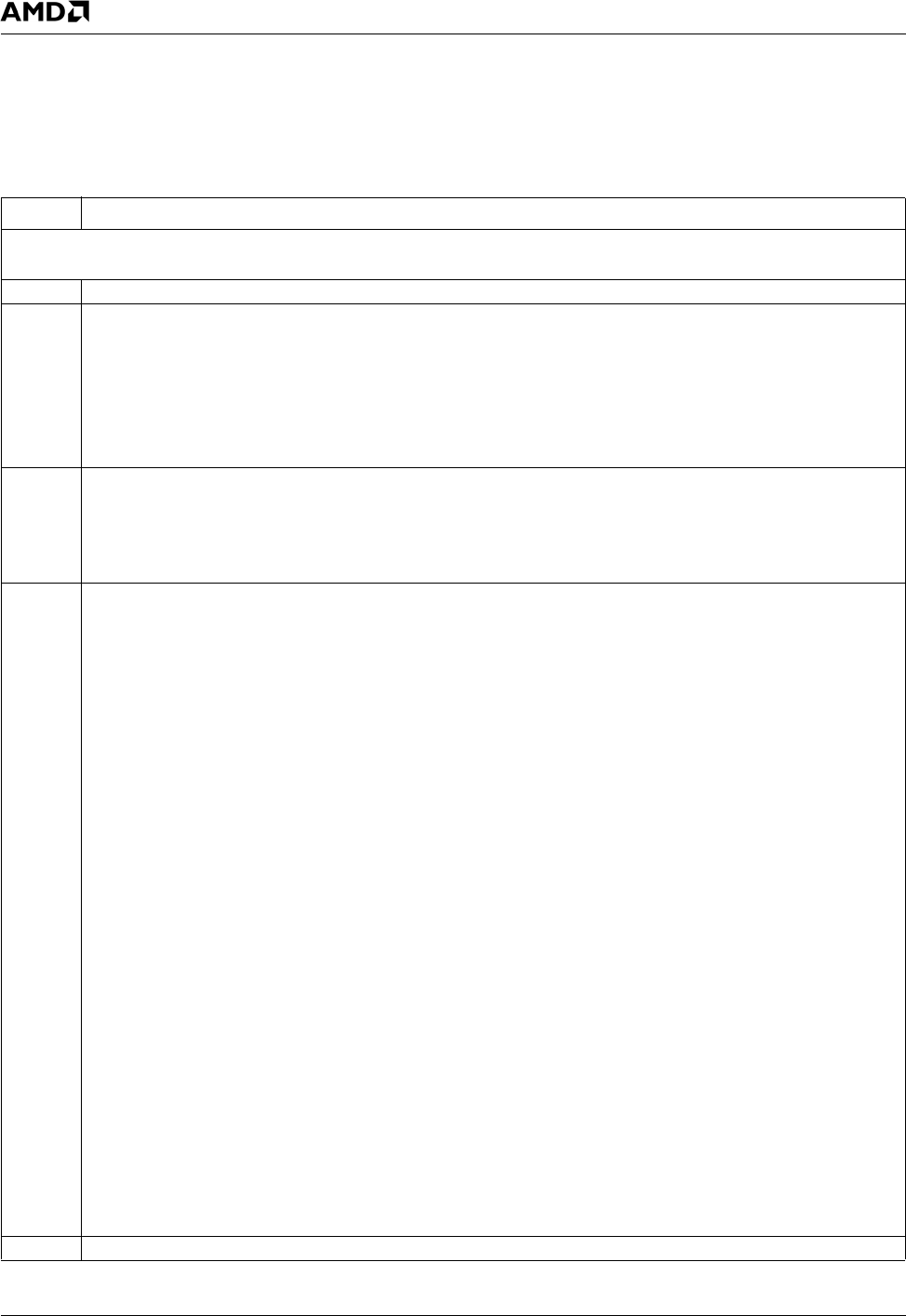

4.2 Multiplexing, Interrupt Selection, and Base Address Registers

The registers described inTable 4-2 are used to determine

general configuration for the SC3200. These registers also

indicate which multiplexed signals are issued via balls from

which more than one signal may be output. For more infor-

mation about multiplexed signals and the appropriate con-

figurations, see Section 3.1 "Ball Assignments" on page 27.

Table 4-2. Multiplexing, Interrupt Selection, and Base Address Registers

Bit Description

Offset 30h-33h Pin Multiplexing Register - PMR (R/W) Reset Value: 00000000h

This register configures pins with multiple functions. See Section 3.1 on page 27 for more information about multiplexing information.

31:30 Reserved: Always write 0.

29 Test Signals. Selects ball functions.

Ball # 0: Internal Test Signals 1: Internal Test Signals

Name Add’l Dependencies Name Add’l Dependencies

D28 / AH3 PLL2B None TEST0 None

C28 / AG4 PLL6B None TEST1 None

B29 / AJ1 PLL5B None TEST2 None

AL16 / V30 GXCLK See PMR[23] TEST3 PMR[23] = 0

28 Test Signals. Selects ball function.

Ball # 0: AC97 Signal 1: Internal Test Signal

Name Add’l Dependencies Name Add’l Dependencies

AJ4 / E28 SIN2 None SDTEST3 See Note.

Note: If this bit is set, PMR[8] and PMR[18] must be set by software.

27 FPCI_MON (Fast-PCI Monitoring). Selects Fast-PCI monitoring output signals instead of Parallel Port signals.

Fast-PCI monitoring output signals can be enabled in two ways: by setting this bit to 1 or by strapping FPCI_MON (ball A4)

high. (The strapped value can be read back at MCR[30].) Listed below is how these two options work together and the sig-

nals that are enabled (enabling overrides add’l dependencies except FPCI_MON = 1). Note that the FPCI monitoring signals

that are muxed with Audio signals are not enabled via this bit. They are only enabled using the strap option.

PMR[27] FPCI_MON

0 0 Disable all Fast-PCI monitoring signals

0 1 Enable all Fast-PCI monitoring signals

1 0 Enable Fast-PCI monitoring signals muxed with Parallel Port signals only

1 1 Enable all Fast-PCI monitoring signals

Ball #

FPCI_MON Other Signal Add’l Dependencies

U3 / B18 FPCICLK ACK#+TFTDE See PMR[23]

U1 / A18 F_AD7 PD7+TFTD13 See PMR[23]

V3 / A20 F_AD6 PD6+TFTD1 See PMR[23]

V2 / C19 F_AD5 PD5+TFT11 See PMR[23]

V1 / C18 F_AD4 PD4+TFTD10 See PMR[23]

W2 / C20 F_AD3 PD3+TFTD9 See PMR[23]

W3 / D20 F_AD2 PD2+TFTD8 See PMR[23]

Y1 / A21 F_AD1 PD1+TFTD7 See PMR[23]

AA1 / C21 F_AD0 PD0_TFTD5 See PMR[23]

T4 / C17 F_C/BE3# SLCT+TFTD15 See PMR[23]

T3 / D17 F_C/BE2# PE+TFTD14 See PMR[23]

T1 / B17 F_C/BE1# BUSY/WAIT#+TFTD3 See PMR[23]

AA3 / D21 F_C/BE0# ERR#+TFTD4 See PMR[23]

AB1 / A22 F_FRAME# STB#/WRITE#+TFTD7 See PMR[23]

W1 / B20 F_IRDY# SLIN#/ASTRB#+TFTD16 See PMR[23]

AB2 / D22 INTR_O AFD#/DSTRB#+TFTD2 See PMR[23]

Y3 / B21 SMI_O INIT#+TFTD5 See PMR[23]

AL15 / V31 F_DEVSEL# GPIO16+PC_BEEP FPCI_MON = 1 and see PMR[0]

AJ15 / U29 F_STOP# AC97_RST# FPCI_MON = 1

AK14 / U31 F_GNT0# SDATA_IN FPCI_MON = 1

AL14 / U30 F_TRDY# BIT_CLK FPCI_MON = 1

26 Reserved. Always write 0.