5–22 Internal Processor Registers

Alpha 21264/EV67 Hardware Reference Manual

Ibox IPRs

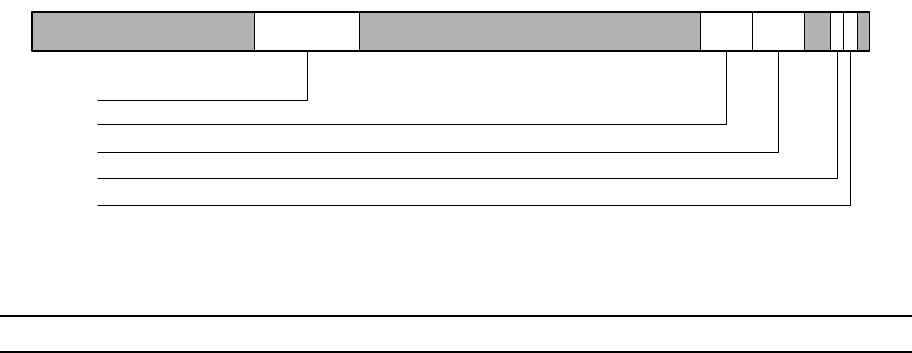

Figure 5–24 Process Context Register

Table 5–14 describes the process context register fields.

Table 5–14 Process Context Register Fields Description

Name Extent Type Description

Reserved [63:47] ——

ASN[7:0] [46:39] RW Address space number.

Reserved [38:13] — —

ASTRR[3:0] [12:9] RW AST request register—used to request AST interrupts in

each of the four processor modes.

To generate a particular AST interrupt, its corresponding

bits in ASTRR and ASTER must be set, along with the

ASTE bit in IER.

Further, the value of the current mode bits in the PS register

must be equal to or higher than the value of the mode associ-

ated with the AST request.

The bit order with this field is:

User Mode 12

Supervisor Mode 11

Executive Mode 10

Kernel Mode 9

ASTER[3:0] [8:5] RW AST enable register—used to individually enable each of

the four AST interrupt requests.

The bit order with this field is:

User Mode 8

Supervisor Mode 7

Executive Mode 6

Kernel Mode 5

Reserved [4:3] — —

63 39 938 84746 5413 312 2 1 0

ASN[7:0]

ASTRR[3:0]

ASTER[3:0]

FPE

PPCE

LK

99

-

003

2A