11–4 Testability and Diagnostics

Alpha 21264/EV67 Hardware Reference Manual

TestStat_H Pin

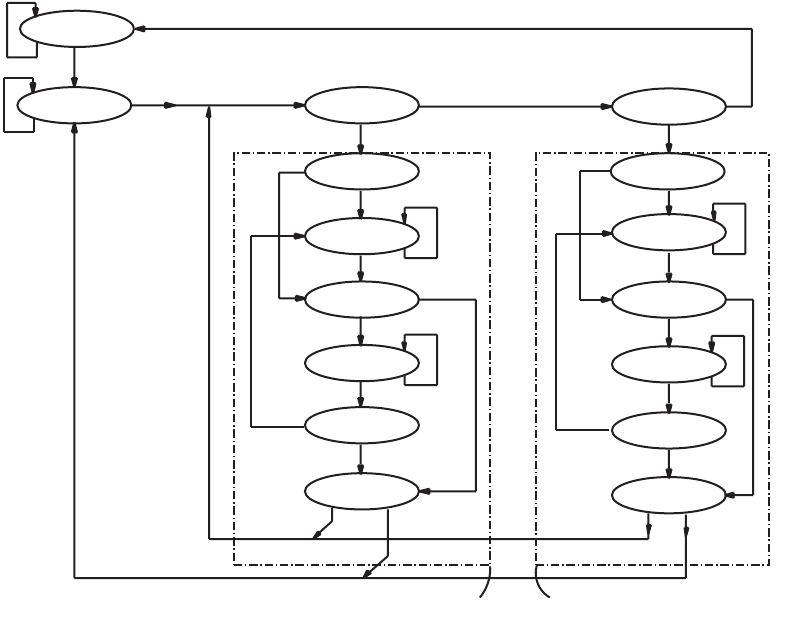

Figure 11–1 TAP Controller State Machine

11.4 TestStat_H Pin

The TestStat_H pin serves two purposes. During power-up, it indicates BiST pass/fail

status. After power-up, it indicates the 21264/EV67 timeout event.

The system reset forces TestSt at_ H to low. Tbox forces it high during the internal BiST

and array initialization operations. During result extraction (DoResult state), the Tbox

drives it low for 16 cycles. After that, the pin remains low if the BiST has passes, other-

wise, it is asserted high and remains high until chip is reset again. Figure 11–2 pictori-

ally shows the behavior of the pin during the power-up operations.

Note: A system designer may sample the TestStat_H pin on the first rising edge

of the SromClk_H pin to determine BiST results. After the power-up dur-

ing the normal chip operation, whenever the 21264/EV67 does not retire an

instruction for 2K CPU cycles, the pin is asserted high for 3 CPU cycles.

Test Logic

Reset

Run-Test/Idle Select-IR-Scan

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

Select-DR-Scan

Capture-DR

Shift-DR

Exit1-DR

Pause-DR

Exit2-DR

Update-DR

Capture-IR

Shift-IR

Exit1-IR

Pause-IR

Exit2-IR

Update-IR

Scan SequenceScan Sequence

Values

shown

are for

TMS.

MK145508.AI4