Alpha 21264/EV67 Hardware Reference Manual

Internal Architecture 2–3

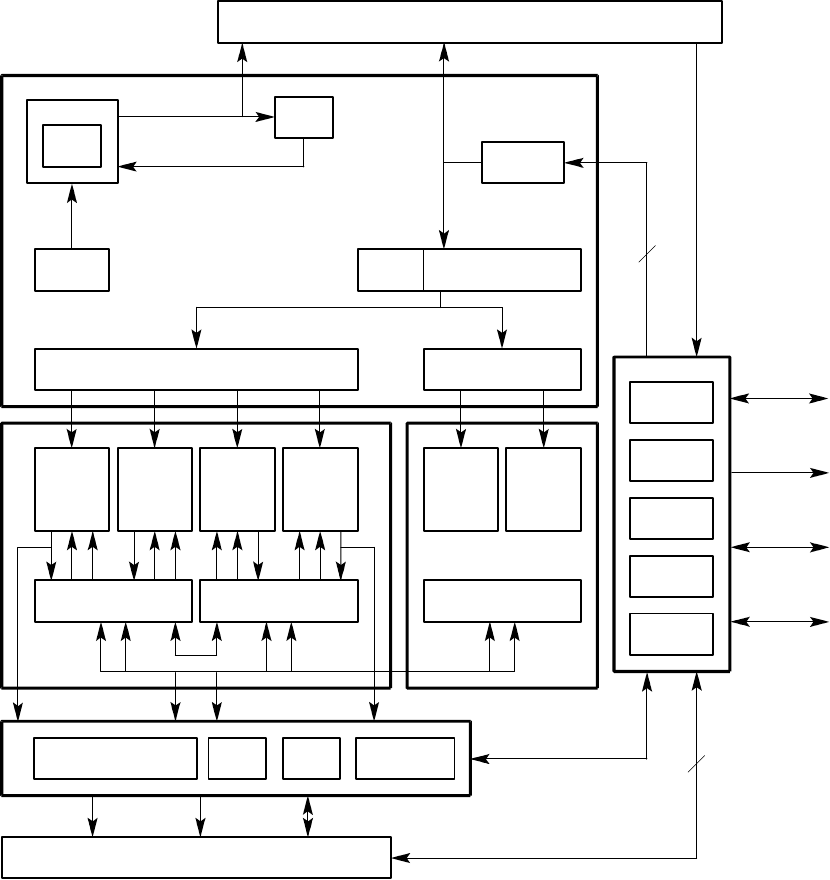

21264/EV67 Microarchitecture

Figure 2–1 21264/EV67 Block Diagram

2.1.1.2 Branch Predictor

The branch predictor is composed of three units: the local, global, and choice predic-

tors. Figure 2–2 shows how the branch predictor generates the predicted branch

address.

INT

UNIT

1

(U1)

Address

ALU 1

(L1)

Address

ALU 0

(L0)

Branch

Predictor

VPC

Queue

INT

UNIT

0

(U0)

Integer Registers 1

(80 Registers)

Integer Registers 0

(80 Registers)

Ebox

FP

ADD

DIV

SQRT

FP

MUL

FP Registers

(72 Re

g

isters)

Fbox

Dual-Ported Data Cache

Physical

Address

Mbox

DTB

(Dual-ported, 128-entry)

Load

Queue

Store

Queue

Miss Address

File

Arbiter

Victim

Buffer

IOWB

Duplicate

Tag Store

Probe

Queue

Cache

Data

128

Cache

Index

20

System

Bus

64

System

Address

15

128

Cbox

FP Issue Queue

(15 Entries)

Integer Issue Queue

(20 Entries)

Ibox

Decode and

Rename Registers

Retire

Unit

ITB

Predecode

Fetch Unit

Next Address

Virtual Address

Four

Instructions

Instruction Cache

128

Physical

Address

Data

Data

FM-

056

42-AI4