Intel

®

820E Chipset

R

104 Design Guide

2.22.1.1. Bus Topologies

The LAN Connect Interface can be configured in several topologies, as follows:

• Direct point-to-point connection between the ICH2 and the LAN component

• Dual footprint (see Section 2.22.6.)

• LOM/CNR implementation

2.22.1.2. Point-to-Point Interconnect

The following are guidelines for a single-solution motherboard. Either the Intel 82562EH component,

Intel

82562ET component or CNR is installed.

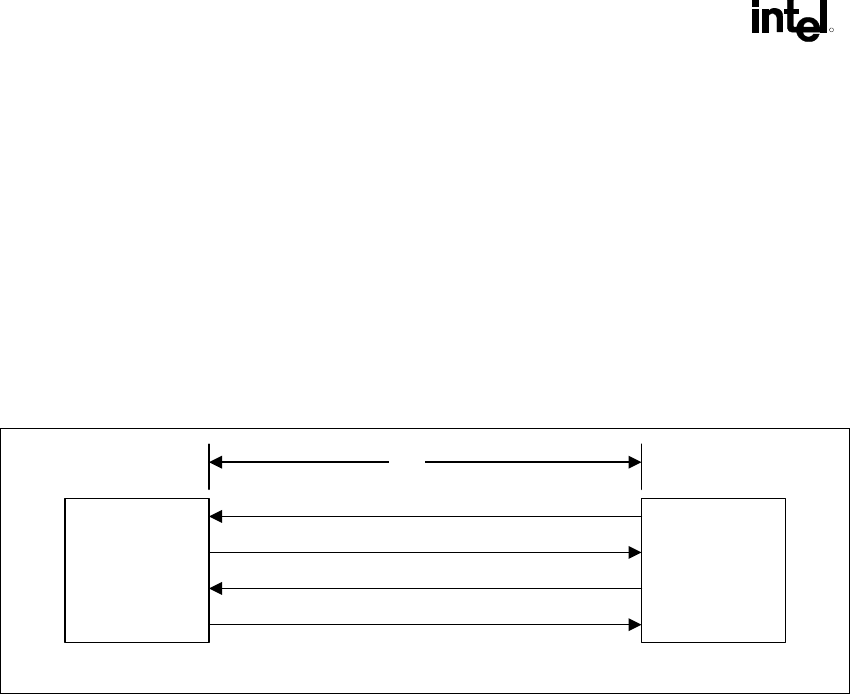

Figure 65. Single-Solution Interconnect

IO_subsys_single_sol_interconn

ICH2

Platform LAN

Connect

(PLC)

LAN_TXD[2:0]

LAN_RXD[2:0]

LAN_RSTSYNC

LAN_CLK

L

Length requirements for Figure 65:

Intel 82562EH: L = 4.5 inches to 10.0 inches (Signal lines LAN_RXD[2:1] and LAN_TXD[2:1] are

not connected.)

Intel 82562ET: L = 3.5 inches to 10.0 inches

CNR*: L = 3.0 inches to 9.0 inches (0.5 inch to 3.0 inches on card)

2.22.1.3. LOM/CNR Interconnect

The following guidelines enable an all-inclusive motherboard solution. This layout combines the LOM,

dual footprint, and CNR solutions. The resistor pack ensures that either a CNR option or a LAN-on-

motherboard option can be implemented at one time. The following figures show a model of this. The

recommended trace routing lengths are shown in Table 23.