Intel

®

820E Chipset

R

Design Guide 131

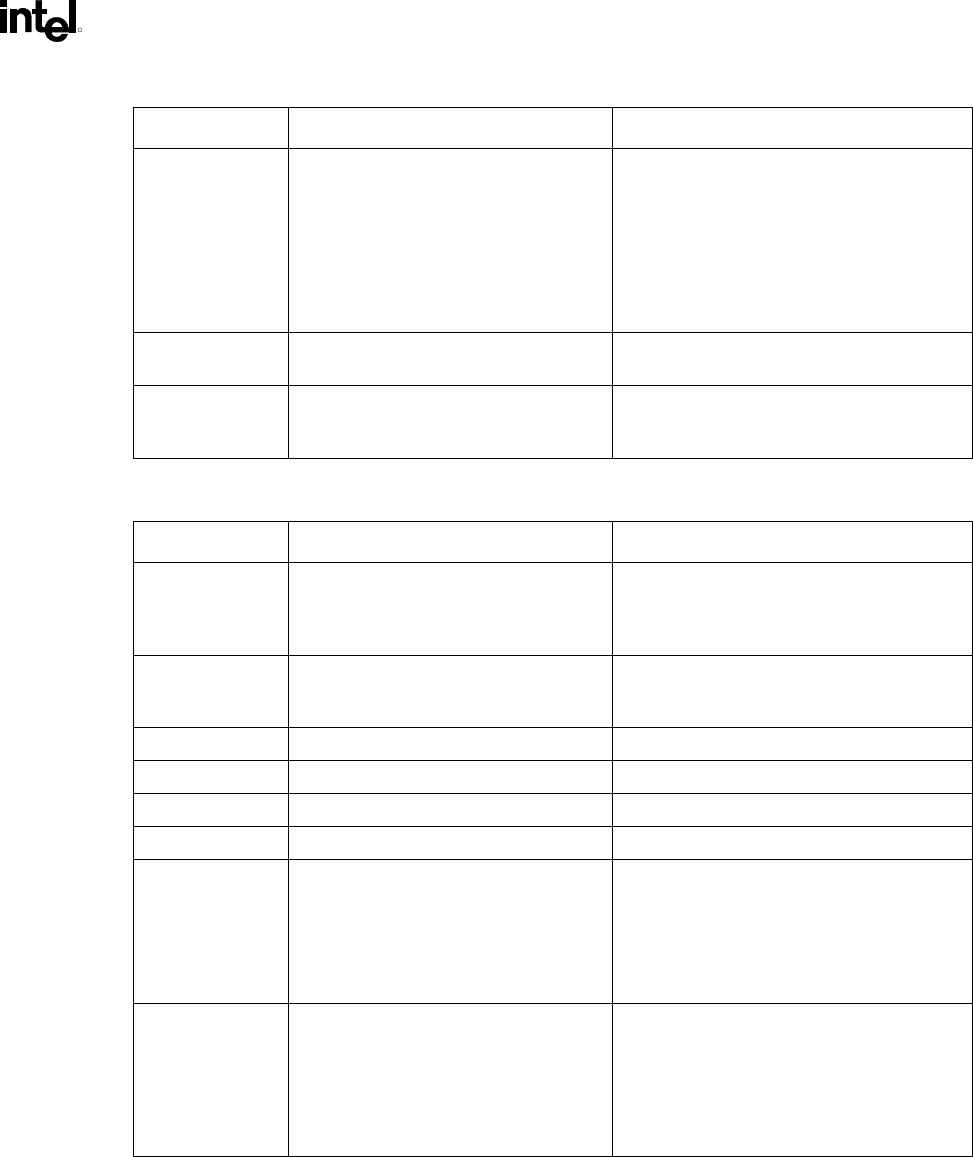

Table 39. Miscellaneous Signals

Checklist Items Recommendations Reason/Effect

SPKR No extra pull-up resistors

Effective impedance due to speaker and

codec circuitry must be greater than 50

k

Ω, or a means to isolate the resistive

load from the signal while PWROK is low

must be found.

Has integrated pull-up with a resistance

between 18 kΩ and 42 kΩ. The integrated pull-

up is enabled only during boot/reset for

strapping functions. At all other times, the pull-

up is disabled.

A low effective impedance may cause the

TCO Timer Reboot function to be erroneously

disabled.

TP[0] Requires external pull-up resistor to

VCCSUS3.3.

This signal is used for BATLOW in mobile, but

it is not required for desktop.

FS[0] Route to a test point. ICH2 contains an integrated pull-up for this

signal. Test point used for manufacturing

appears in XOR tree.

Table 40. Power

Checklist Items Recommendations Reason/Effect

V_CPU_IO[1:0] The power pins should be connected to

the proper power plane for the

processor's CMOS compatibility signals.

Use one 0.1 µF decoupling cap.

Used to pull-up all processor I/F signals

Vcc RTC No clear CMOS jumper on Vcc RTC. Use

a jumper on RTCRST# or a GPI, or use

safe-mode strapping for clear CMOS

Vcc 3.3 V Requires six 0.1 µF decoupling caps

Vcc Sus 3.3 V Requires one 0.1 µF decoupling cap.

Vcc 1.8 V Requires two 0.1 µF decoupling caps.

Vcc Sus 1.8 V Requires one 0.1 µF decoupling cap.

5V_REF SUS Requires one 0.1 µF decoupling cap.

V5REF_SUS affects only the 5 V

tolerance for USB OC[3:0] ins, and it can

be connected to VccSUS3_3 if 5 V

tolerance is not required for these

signals.

5V_REF 5 V

REF

is the reference voltage for 5 V-

tolerant inputs in the ICH2. The

VREF[2:1] pins must be tied together. 5

V

REF

must power up before or

simultaneously with Vcc 3_3. It must

power down after or simultaneously with

Vcc 3_3.

Refer to Figure 73, which shows an example

circuit schematic that may be used to ensure

the proper 5 VREF sequencing.