Intel

®

820E Chipset

R

Design Guide 85

2.13. AC’97

The ICH2 implements an AC’97 2.1-compliant digital controller. Any codec attached to the ICH2

AC-link also must be AC’97 2.1 compliant. Please contact your codec IHV for information on

2.1-compliant products. The AC’97 2.1 specification is on the following Intel web page:

http://developer.intel.com/pc-supp/platform/ac97/index.htm

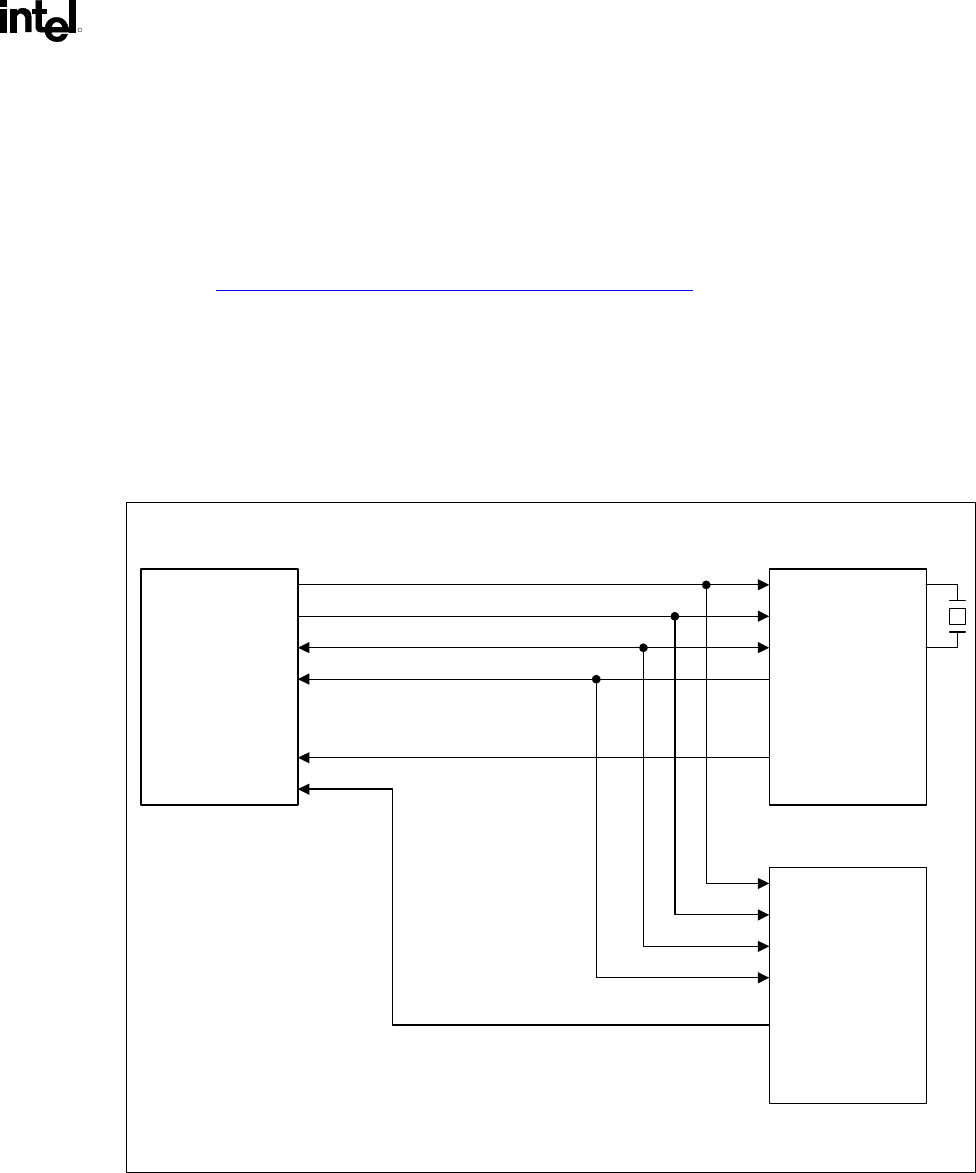

The AC-link is a bi-directional, serial PCM digital stream. It handles multiple input and output data

streams as well as control register accesses, employing a time division multiplexed (TDM) scheme. The

AC-link architecture provides for data transfer through individual frames transmitted serially. Each frame

is divided into 12 outgoing and 12 incoming data streams, or slots. The architecture of the ICH2 AC-link

allows a maximum of two codecs to be connected. The following figure shows a two-codec topology of

the AC-link for the ICH2.

Figure 50. ICH2 AC’97– Codec Connection

AC '97 2.1

controller section

of ICH2

Digital AC '97

2.1 controller

Primary codec

Secondary codec

AC / MC

AC / MC / AMC

ICH2_AC97_codec_conn

SDIN 0

SDIN 1

RESET#

SDOUT

SYNC

BIT_CLK

The AC’97 interface can be routed using 5 mil traces, with 5 mil space between traces. The maximum

length from ICH2 to CODEC/CNR is 14 inches, in a tee topology. This assumes that a CNR riser card

implements its audio solution with a maximum trace length of 4 inches for the AC-link. The trace

impedance should be as follows: Z

0

= 60 Ω ± 15%.