Intel

®

820E Chipset

R

Design Guide 189

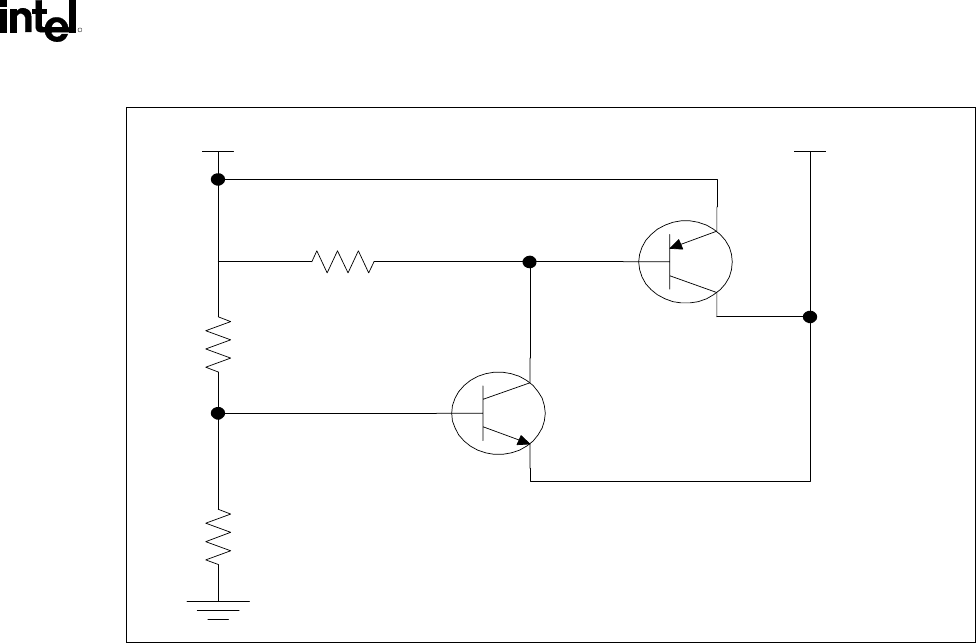

Figure 103. Example 1.8V/3.3V Power Sequencing Circuit

Q1

PNP

Q2

NPN

220

220

470

+3.3V

+1.8V

When analyzing systems that may be “marginally compliant” with the 2 V Rule, pay close attention to the

behavior of the ICH2’s RSMRST# and PWROK (also LAN_PWROK in ICH2-m) signals, since these

signals control the internal isolation logic between the various power planes, as follows:

• RSMRST# controls the isolation between the RTC well and the resume wells.

• PWROK controls the isolation between the resume wells and main wells.

• LAN_PWROK controls the isolation between the LAN wells and the resume wells (applies only to

ICH2-m).

If one of these signals goes high while one of its associated power planes is active and the other is not, a

leakage path will exist between the active and inactive power wells. This could result in high, possibly

damaging, internal currents.

6.1.4. 3.3V/V5REF Sequencing

V5REF is the reference voltage for 5 V tolerance on inputs to the ICH2. V5REF must be powered up

before or simultaneously to Vcc3_3. It must also power down after or simultaneous to Vcc3_3. The rule

must be followed in order to ensure the safety of the ICH2. If the rule is violated, internal diodes will

attempt to draw power sufficient to damage the diodes from the Vcc3_3 rail. Figure 104 shows a sample

implementation of how to satisfy the V5REF/3.3V sequencing rule.

This rule also applies to the stand-by rails, but in most platforms, the VccSus3_3 rail is derived from the

VccSus5 and therefore, the VccSus3_3 rail will always come up after the VccSus5 rail. As a result,

V5REF_Sus will always be powered up before VccSus3_3. In platforms that do not derive the

VccSus3_3 rail from the VccSus5 rail, this rule must be comprehended in the platform design.

As an additional consideration, during suspend the only signals that are 5V tolerant are USBOC. If these

signals are not needed during suspend, V5REF_Sus can be hooked to the VccSus3_3 rail.