Intel

®

820E Chipset

R

Design Guide 149

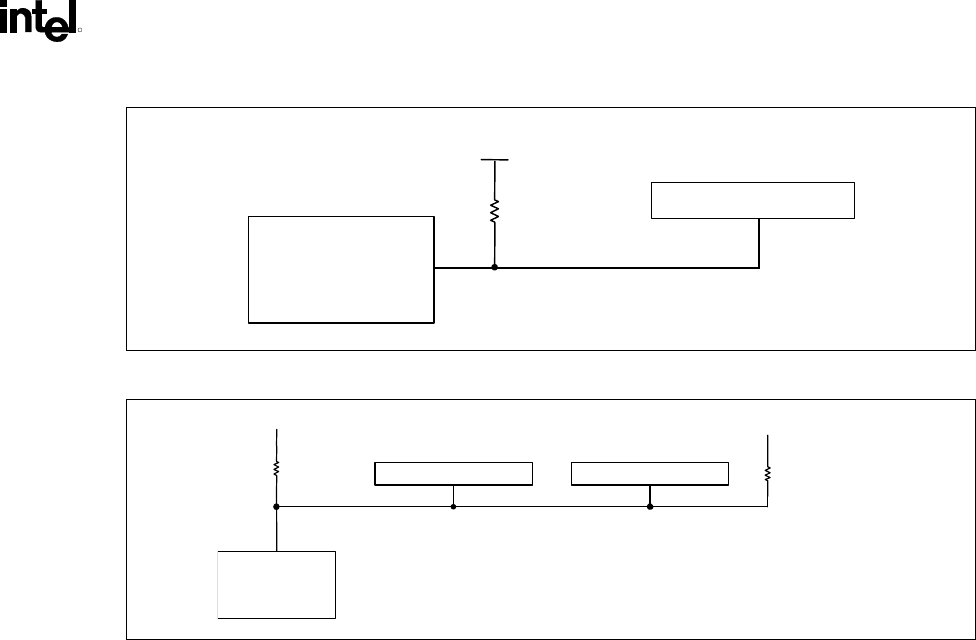

Figure 74. PICD[1,0] Uniprocessor Topology

ICH2

Intel

®

PGA370

Z

0

= 60

Ω

± 15%

1.5

150

Ω

picd_uniprocessor_topo

Figure 75. PICD[1,0] Dual-Processor Topology

ICH2

Intel® PGA370

Z

0

= 60 Ω

± 15%

1.5 V

300–330 Ω

Intel PGA370

1.5 V

300 –330 Ω

picd_dual-processor_topo

3.2.5. Post-Layout Simulation

After layout, extract the interconnect information for the board from the CAD layout tools. Run

simulations to verify that the layout satisfies the timing and noise requirements. A small amount of

“tuning” may be required. Experience at Intel has shown that sensitivity analysis dramatically reduces the

amount of tuning required. Post-layout simulations should take into account the expected variation for all

interconnect parameters.

Intel specifies signal integrity at the device pads and therefore recommends running simulations at the

device pads for signal quality. However, Intel specifies core timings at the device pins, so simulation

results at the device pins should be used later to correlate the simulation performance with actual system

measurements.

3.2.5.1. Intersymbol Interference

Intersymbol interference (ISI) refers to the distortion or change in the waveform shape caused by the

voltage and transient energy on the network when the driver begins its next transition.

Intersymbol interference occurs when transitions in the current cycle interfere with transitions in

subsequent cycles. ISI can occur when the line is driven high, low, and high in consecutive cycles. (The

opposite case also is valid.) When the driver drives high on the first cycle and low on the second cycle,

the signal may not settle to the minimum V

OL

before the next rising edge is driven. This results in

improved flight times in the third cycle. Intel performed ISI simulations for the topology given in this

section by comparing flight times for the first and third cycles. ISI effects do not necessarily span only

3 cycles, so it may be necessary to simulate beyond 3 cycles for certain designs. After simulating and

quantifying the ISI effects, adjust the timing budget accordingly to take into consideration these

conditions.