Intel

®

820E Chipset

R

Design Guide 163

4. Clocking

4.1. Clock Generation

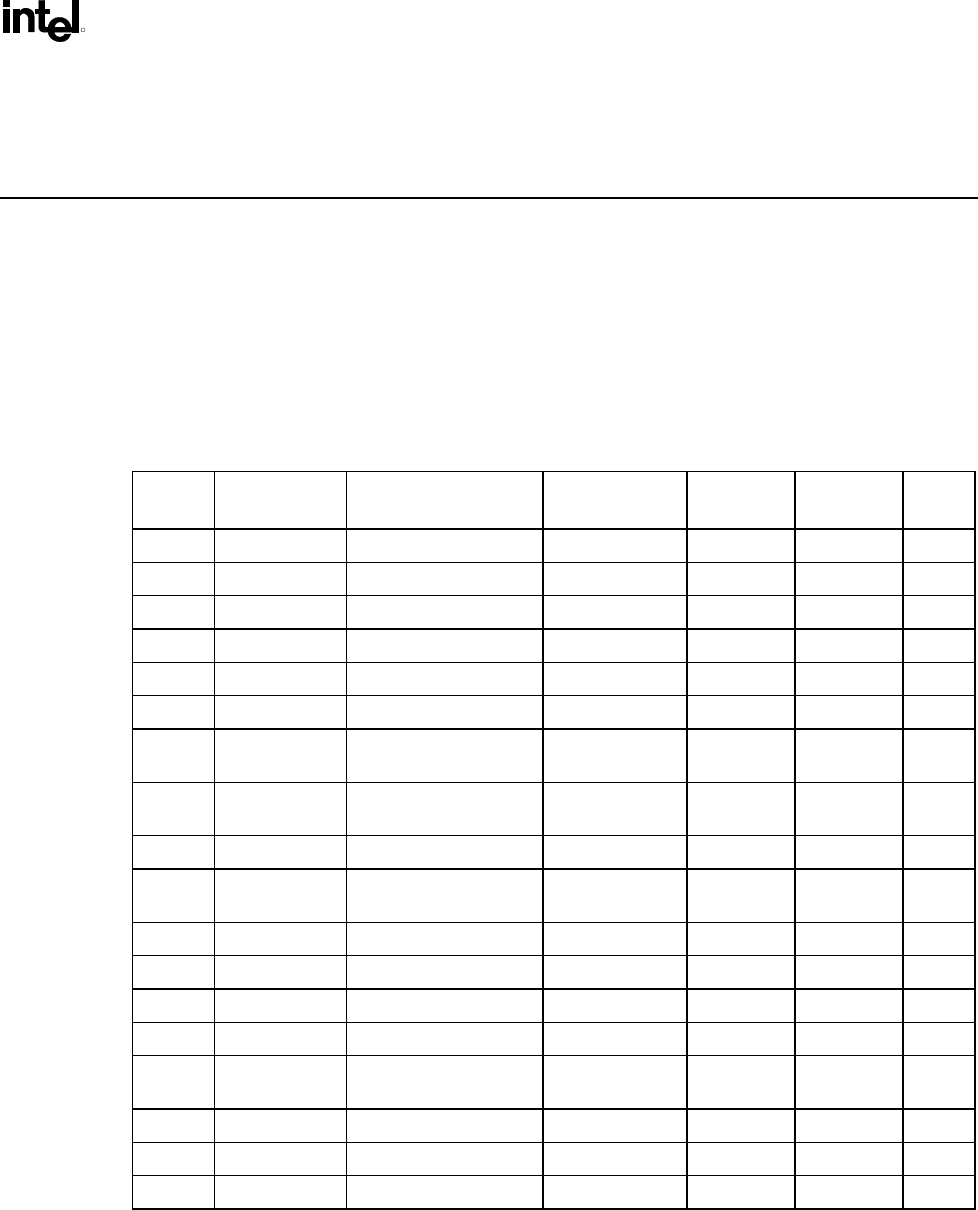

Two clock generator components are required in an Intel 820E chipset-based system. The Direct

RDRAM clock generator (DRCG) generates clock for the Direct RDRAM interface, while the CK133

component generates clocks for the rest of the system. Clock synthesizers that meet the Intel CK98 Clock

Specification are suitable for an Intel 820E chipset-based system. The CK133 generates the clocks listed

in the following table.

Table 55. Intel

®

820E Chipset Platform System Clocks

Number Name on CK133 Used for Routed to Name on

Receiver

Frequency Voltage

4 CPUCLK[0–3] System bus clock 2 processors CLK 100/133 MHz 2.5 V

MCH HCLKIN

ITP BCLK

3 APIC[0–2] APIC bus clock 2 processors PICCLK 33 MHz 2.5 V

ICH2 APICCLK

8 PCICLK[1–7,F] PCI bus clock 5 PCI devices CLK 33 MHz 3.3 V

PCI, LPC, FWH Flash

BIOS bus clock

ICH2 PCICLK

FWH Flash BIOS I/F

clock

FWH Flash BIOS CLK

LPC I/F clock LPC CLK

4 3V66[0–3] Hub interface/AGP bus

clock

MCH CLK66 66 MHz 3.3 V

Hub interface clock ICH2 CLK66

AGP bus clock AGP device/ slot CLK

Unused N/A N/A

2 REF[0–1] Internal ICH2 logic ICH2 CLK14 14 MHz 3.3 V

Internal super I/O logic Super I/O Vendor

specific

1 48MHz USB ICH2 CLK48 48 MHz 3.3 V

2 CPU_DIV2[0–1] DRCG reference clock DRCG REFCLK 50/66 MHz 2.5 V

Unused N/A N/A

The CK133 is a mixed-voltage component. Some of the output clocks are 3.3 V, and some of the output

clocks are 2.5 V. As a result, the CK133 device requires both 3.3 V and 2.5 V. These power supplies

should be a clean as possible. Noise in the power delivery system for the clock driver can cause noise on

the clock lines.