Intel

®

820E Chipset

R

52 Design Guide

It is necessary to compensate for the slight difference in electrical characteristics between a dummy via

and a real via. Refer to the following section for more information on via compensation.

2.7.2.7. Via Compensation

As described in Section 2.7.2.1, all signals must have the same number of vias. As a result, each trace

will have one via (near the BGA pad) because some RSL signals must be routed on the bottom of the

motherboard. Therefore, it is necessary to place a dummy via on all signals that are routed on the top

layer. Because the electrical characteristics of a dummy via do not exactly match the electrical

characteristics of a real via, additional compensation must be performed for each signal that has a dummy

via. Each signal with a dummy via must have 25 mils of additional trace length. That is:

Real via = Dummy via + 25 mils of trace length

This 25 mils of additional trace length must be added to each signal routed on the top layer after length

matching, as documented in Section 2.7.2.6.

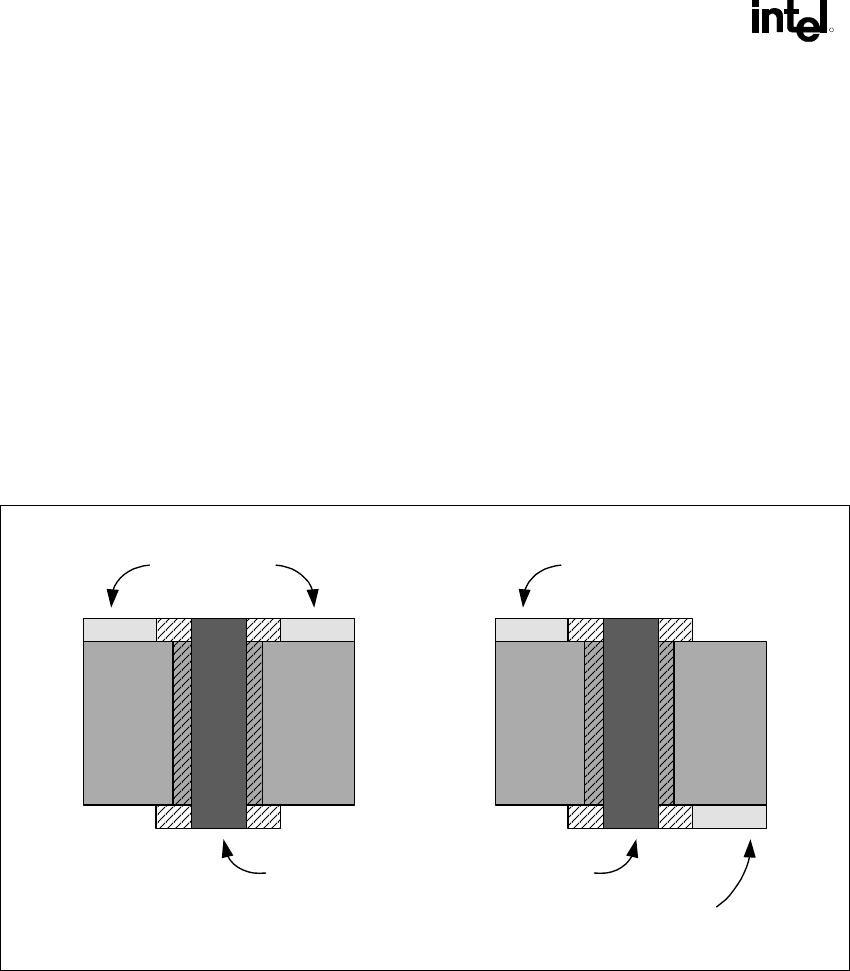

Figure 31. “Dummy” Via vs. “Real” Via

“DUMMY Via”

PCB PCB

“REAL Via”

PCB PCB

Trace

Trace

Via Via

Trace

dum_vias_vs_real.v

2.7.2.8. Length Matching and Via Compensation Example

Table 8 can be used to ensure that the RSL signals are the correct length.

Note: 2000 mils was chosen as an example nominal RSL length.