Intel

®

820E Chipset

R

Design Guide 141

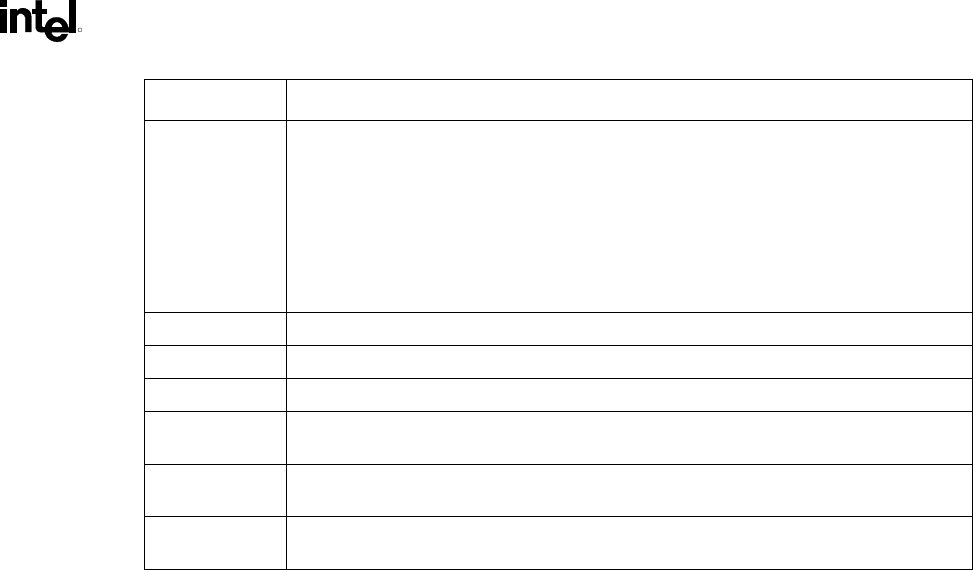

Term Definition

Simultaneous

switching

output (SSO)

effects

Difference in electrical timing parameters and degradation in signal quality caused

by multiple signal outputs simultaneously switching voltage levels (e.g., high to

low), in the direction opposite to a single signal (e.g., low to high) or in the same

direction (e.g., high to low). These are respectively called odd-mode switching and

even-mode switching. This simultaneous switching of multiple outputs creates

higher current swings that may cause additional propagation delay (or “push-out”)

or a decrease in propagation delay (or “pull-in”). These SSO effects may affect the

setup and/or hold times and are not always taken into account by simulations.

System timing budgets should include margin for SSO effects.

Stub Branch from the trunk terminating at the pad of an agent

Test load Intel uses a 50 Ω test load for specifying its components.

Trunk The main connection, excluding interconnect branches, terminating at agent pads

Undershoot Maximum voltage a signal may extend below V

SS

at the processor core pad. See the

respective processor’s datasheet for the undershoot specifications.

Victim A network that receives a coupled crosstalk signal from another network is called

the victim network.

V

REF

guard

band

A guard band (∆V

REF

) defined above and below V

REF

, to provide a more realistic

model accounting for noise, such as crosstalk, V

TT

noise, and V

REF

noise

3.2. AGTL+ Design Guidelines

The following step-by-step guideline was developed for systems based on two processor loads and one

Intel 82820 MCH load. Systems using custom chipsets will require timing analysis and analog

simulations specific to those components.

The guideline recommended in this section is based on experience accumulated at Intel while developing

many different systems based on the Intel

®

Pentium

®

Pro processor family and the Pentium III processor.

First, perform an initial timing analysis and topology definition. Then perform pre-layout analog

simulations, for a detailed picture of a working “solution space” for the design. These pre-layout

simulations help define the routing rules prior to placement and routing. After routing, extract the

interconnect database and perform post-layout simulations to refine the timing and signal integrity

analysis. Validate the analog simulations when actual systems become available. The validation section

describes a method for determining the flight time in the actual system.

Guideline Methodology

• Initial timing analysis

• Determine general topology, layout, and routing.

• Pre-layout simulation

Sensitivity sweep

Monte Carlo Analysis

• Place and route board

Estimate component-to-component spacing for AGTL+ signals.

Lay out and route board.

• Post-layout simulation

Interconnect extraction

Intersymbol interference (ISI), crosstalk, and Monte Carlo Analysis

• Validation

Measurements

Determining flight time