Intel

®

820E Chipset

R

170 Design Guide

4.2.4. DRCG-to-RDRAM Channel

The Direct RDRAM clock signals (CTM/CTM# and CFM/CFM#) are high-speed, impedance-matched

transmission lines. Direct RDRAM clocks begin at the end of the Direct RDRAM channel and propagate

to the controller as CTM/CTM# (see Figure 90), where they loop back as CFM/CFM#. The following

table lists the placement guidelines.

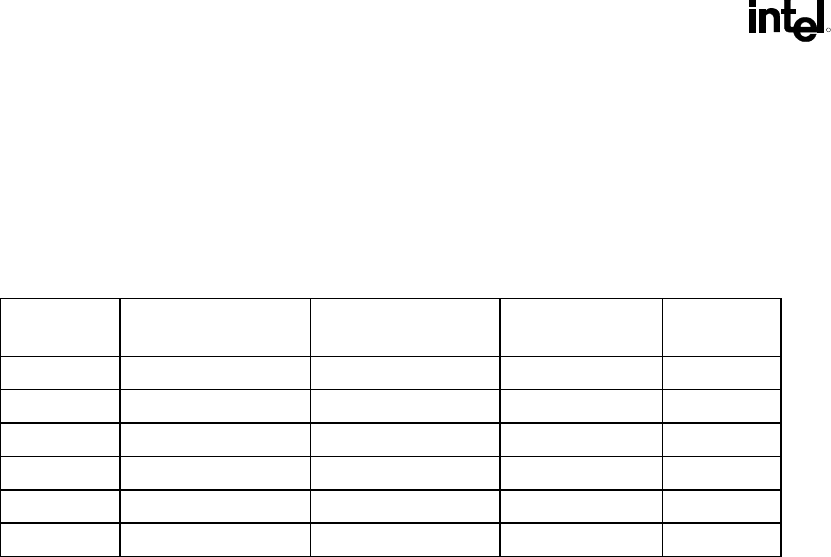

Table 58. Placement Guidelines for Motherboard Routing Lengths (Direct RDRAM* Clock Routing

Length Guidelines)

Clock From To Length (inches) Section

(see Note)

CTM/CTM# DRCG Last RIMM connector 0.000 – 6.000 D

RIMM RIMM 0.400 – 0.450 B

1st RIMM connector Chipset 0.000 – 3.500 A

CFM/CFM# Chipset 1st RIMM connector 0.000 – 3.500 A

RIMM RIMM 0.400 – 0.450 B

Last RIMM connector Termination 0.000 – 3.000 C

NOTES: Refer to Figure 90.

Trace Geometry

In Sections A and D (previous figure), the clock signals (CTM/CTM# and CFM/CFM#) must be 14 mil

wide and routed as shown in Figure 91. For all other sections (B and C), the clock signals must be routed

with 18 mil-wide traces. A 22 mil ground isolation trace must be routed around the clock differential pair

signals. The 22 mil ground isolation traces must be connected to ground with a via every 1 inch. A 6 mil

gap is required between the clock signals and the ground isolation traces. For section A in the previous

Figure 90, 0.021 inch of CLK per 1 inch of RSL trace length must be added to compensate for the

clock’s faster trace velocity, as described in Section 2.7.2.1. The CTM/CTM# and the CFM/CFM#

differential signal pairs must be length-matched to ±2 mils in line section A. For line section B, use the

trace length methods in Section 2.7.2.1. For section D, the trace length matching for CTM/CTM# is ±2

mils, and for section C, ±2 mil trace length matching is required for the CFM/CFM# signals.

The CTM/CTM# signals must be ground-referenced (with a continuous ground island/plane) from the

DRCG to the last RIMM.

4.2.5. Trace Length

For section A in Figure 90 (first RIMM to MCH, and MCH to first RIMM), CTM/CTM# and

CFM/CFM# must be length-matched within ±2 mils. (Exact trace length matching is recommended.)

Package trace compensation (as described in Section 2.7.2.1), via compensation, and RSL signal layer

alternation must also be completed on the clock signals. Additionally, 0.021 inch of CLK per 1 inch of

RSL trace length must be added to compensate for the clock’s faster trace velocity, as described in

Section 2.7.2.1.

For line section B (Figure 90) (RIMM to RIMM), the clock signals must be matched within ±2 mils to

the trace length of every RSL signal. Exact length matching is preferred.