Intel

®

820E Chipset

R

Design Guide 51

All RSL signals must satisfy the following equation:

Equation 2. RDRAM RSL Signal Trace Length Calculation

Package dimension + board trace length = Nominal RSL length ± 10 mils

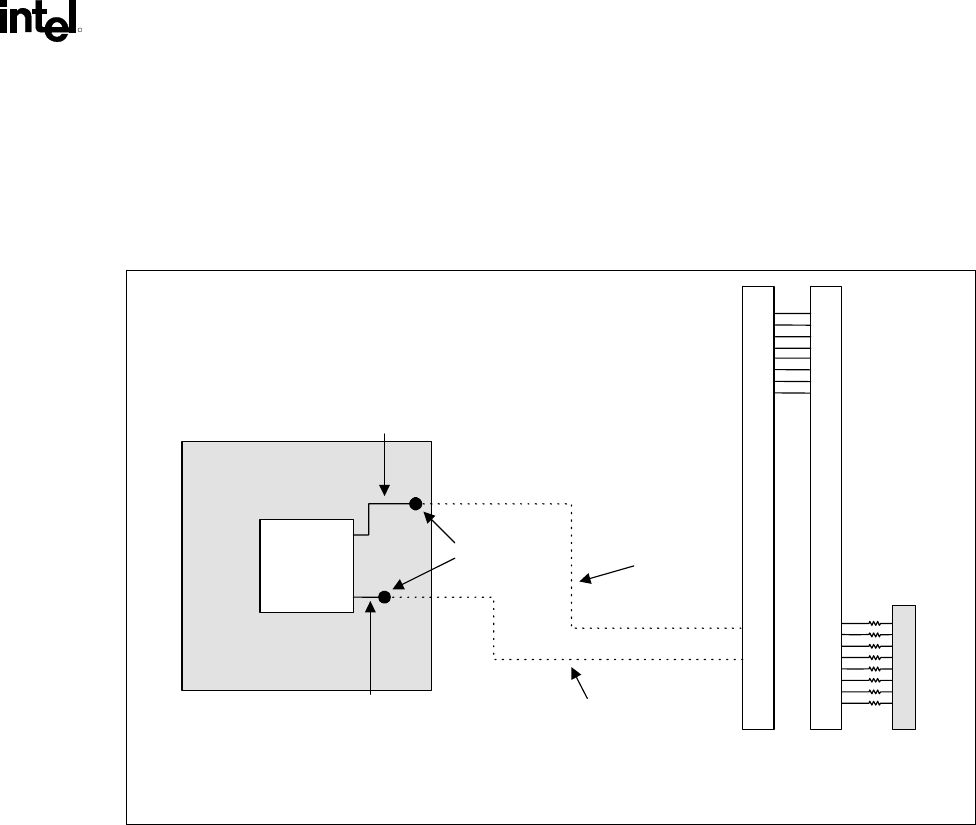

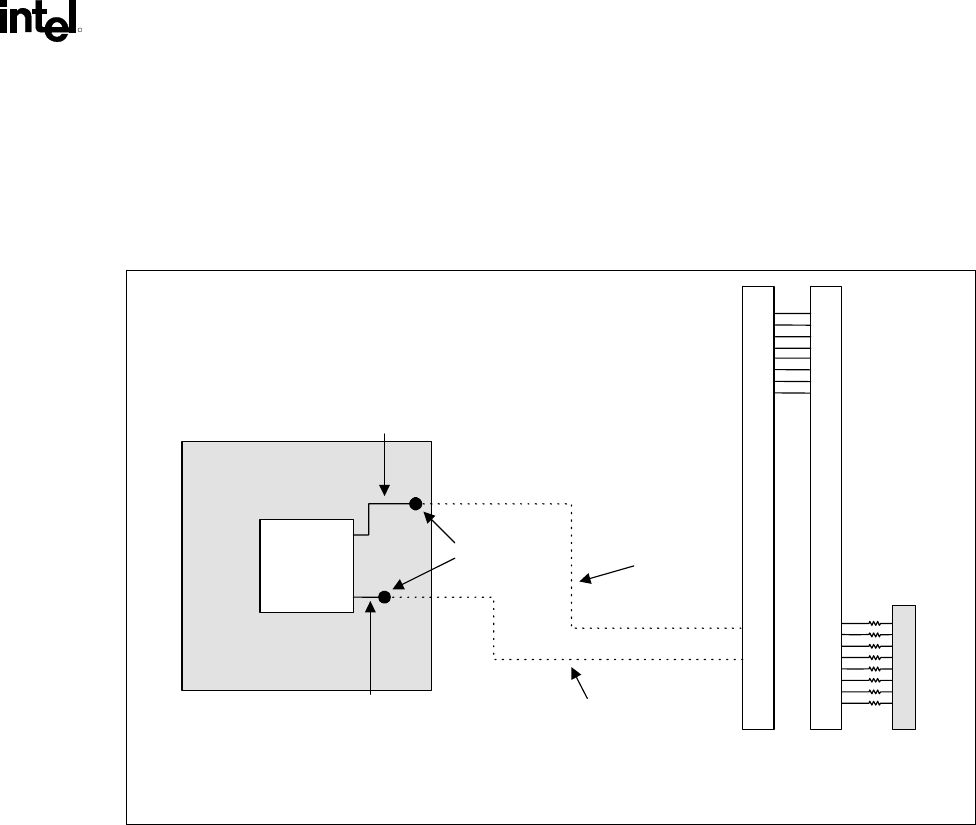

Figure 30. Example of RDRAM Trace Length Matching

MCH

Die

MCH

Die

MCH Package

R

I

M

M

C

o

n

n

e

c

t

o

r

L3

L4

L1

L2

L1, L2: Packa

e dimensions

L3, L4: Board trace length

L1 + L3 = Nominal RSL length ±10 mils

L2 + L4 = Nominal RSL length ±10 mils

Ball

R

I

M

M

C

o

n

n

e

c

t

o

r

rdram_tr_len.vsd

V

t

e

r

m

Note: Refer to the Intel

®

820 Chipset Family: 82820 Memory Controller Hub (MCH) Datasheet for the

component package dimensions.

The RDRAM clocks (CTM, CTM#, CFM, and CFM#) must be longer than the RDRAM signals, due to

their increased trace velocity (because they are routed as a differential pair). To calculate the length for

each clock, the following formula should be used:

Equation 3. RDRAM Clock Signal Trace Length Calculation

Clock length = Nominal RSL signal length (package + board) × 1.021

This formula yields clock signals 21 mils/inch longer than the nominal length. The lengthening of the

clock signals to compensate for their trace velocity change only applies to routing between the MCH and

the first RIMM. The clock signal lengths should be matched to the RSL signals between RIMMs. For

more detailed clock routing guidelines, refer to Chapter 4 Clocking.

The high-speed CMOS signals must be length-matched to the RSL signals within 1200 mils (1.2 inches),

as the result of a timing requirement between the CMOS and RSL signals during NAP Exit and PDN

Exit.