Intel

®

820E Chipset

R

Design Guide 159

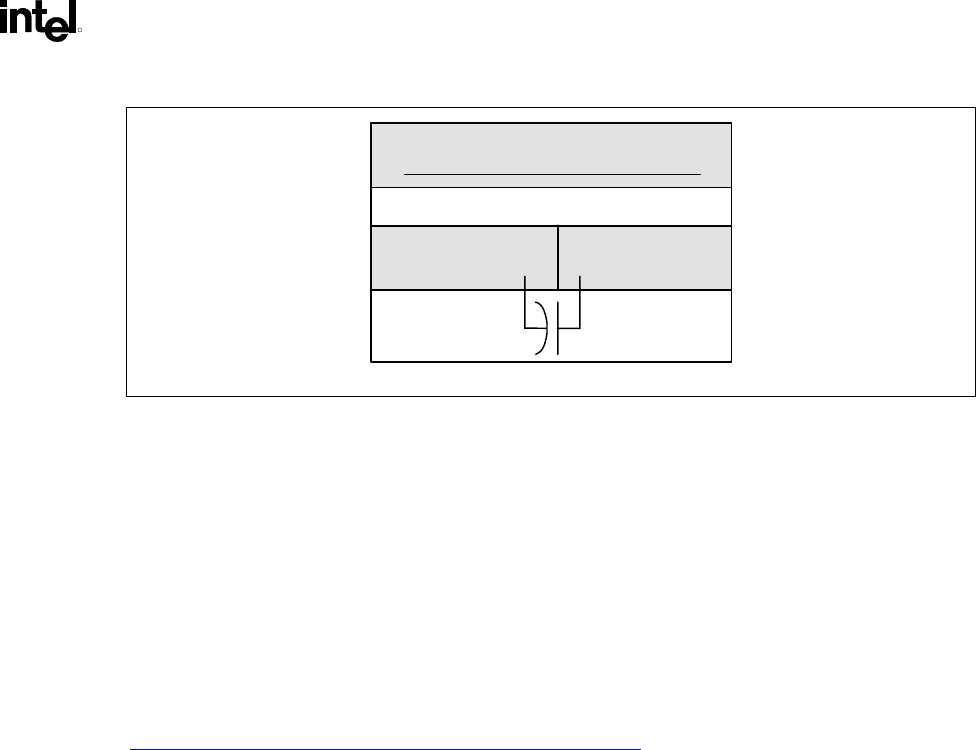

Figure 83. One Layer with Multiple Reference Planes

1lay_Mult_refplane

Ground

Signal Layer A

Power

3.4.3.3. High-Frequency Decoupling

This section contains several high-frequency decoupling recommendations that will improve the return

path for an AGTL+ signal. These design recommendations will very likely reduce the amount of SSO

effects.

Just as layer switching and multiple reference planes can create discontinuities in an AGTL+ signal

return path, discontinuities also may occur when a signal transitions between the baseboard and cartridge.

Therefore, providing adequate high-frequency decoupling across VCC

CORE

and ground within the Intel

PGA370 socket cavity and mounted on the primary side of the motherboard will minimize discontinuity

in the signal’s reference plane at this junction. For the Intel 820E chipset/FC-PGA decoupling guidelines,

refer to the

Intel

®

820 Chipset Design Guide Addendum for the Intel

®

Pentium

®

III Processor for the

PGA370 Socket

. These guidelines can be downloaded from the Intel website at

http://developer.intel.com/design/chipsets/designex/298178.htm

.

Transmission line geometry also influences the return path of the reference plane. The following

decoupling recommendations take this into consideration:

• A signal that transitions from a stripline to another stripline should have close proximity decoupling

among all four reference planes.

• A signal that transitions from a stripline to a microstrip (or vice versa) should have close proximity

decoupling between the three reference planes.

• A signal that transitions from a stripline or microstrip through vias or pins to a component (Intel

82820 MCH, etc.) should have close proximity decoupling across all involved reference planes to

ground for the device.