43

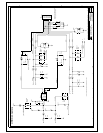

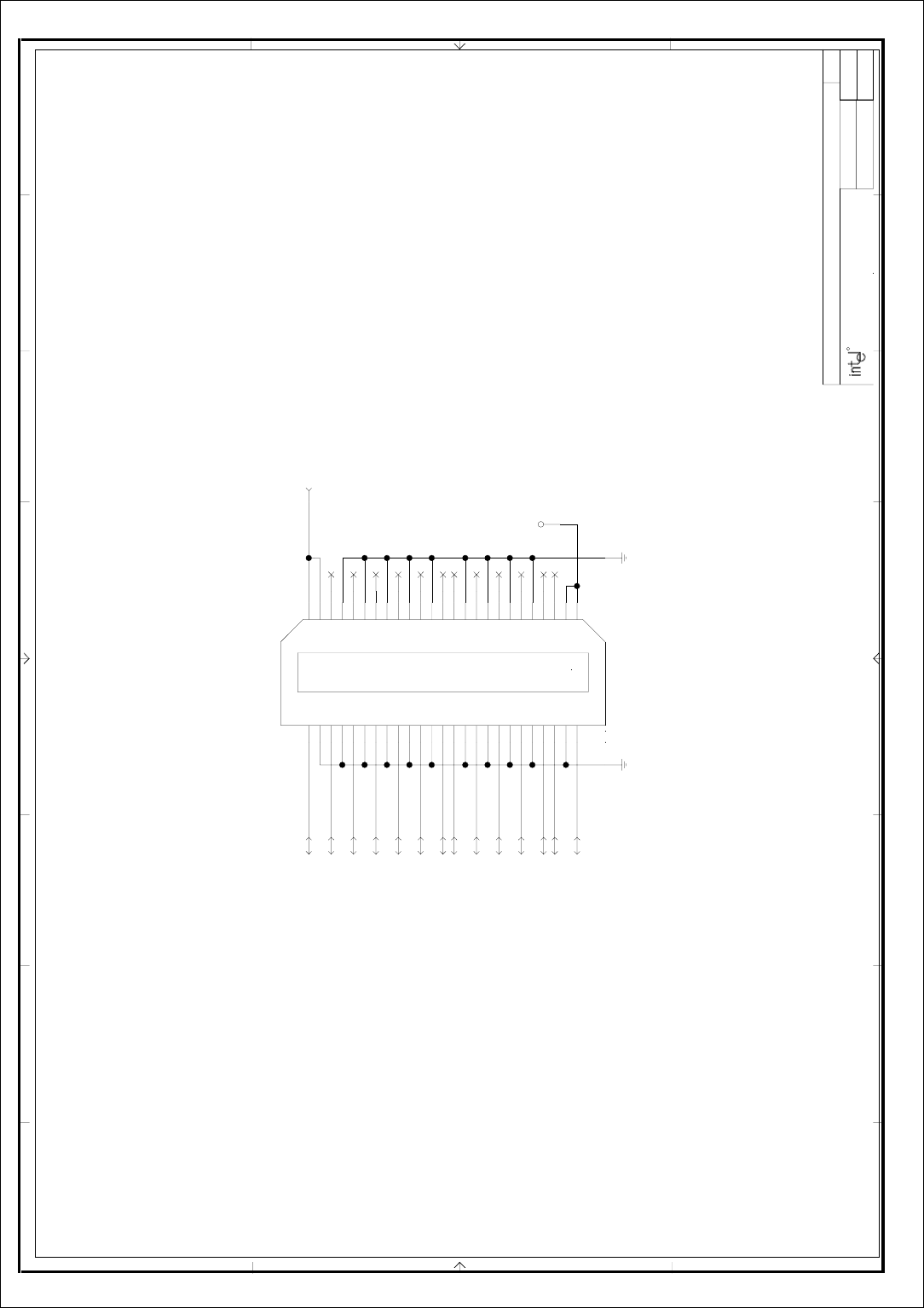

TEST_CLK66

5

HL7

7,8

HL6

7,8

HL5

7,8

HL4

7,8

HL8

7,8

HL10

7,8

HL_STB#

7,8

HL_STB

7,8

HL9

7,8

HL3

7,8

HL2

7,8

HL1

7,8

HL0

7,8

6,8

HUBREF

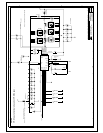

J26

11

50

48

4

2

18

16

14

12

10

8

6

46

44

42

40

38

36

34

32

30

28

26

24

22

20

17

15

13

9

7

5

49

47

45

43

41

39

3

37

35

33

31

29

27

25

23

21

19

1

DRAWN BY:

LAST REVISED: SHEET:

FOLSOM, CALIFORNIA 95630

1900 PRAIRIE CITY ROAD

87 6 54 32 1

A

B

C

D

12345678

D

C

B

A

PCG PLATFORM DESIGN

REV:

0.5

PROJECT:

OF 40

TITLE: INTEL(R) 820E CHIPSET 2 DIMM FCPGA REFERENCE BOARD

R

PCG AE Camino2

VCC1_8

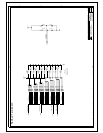

P08-050-SL-A-G

PROBE CONNECTOR

Hub Interface Connector

For debug only.