3-20-2000_10:15 12

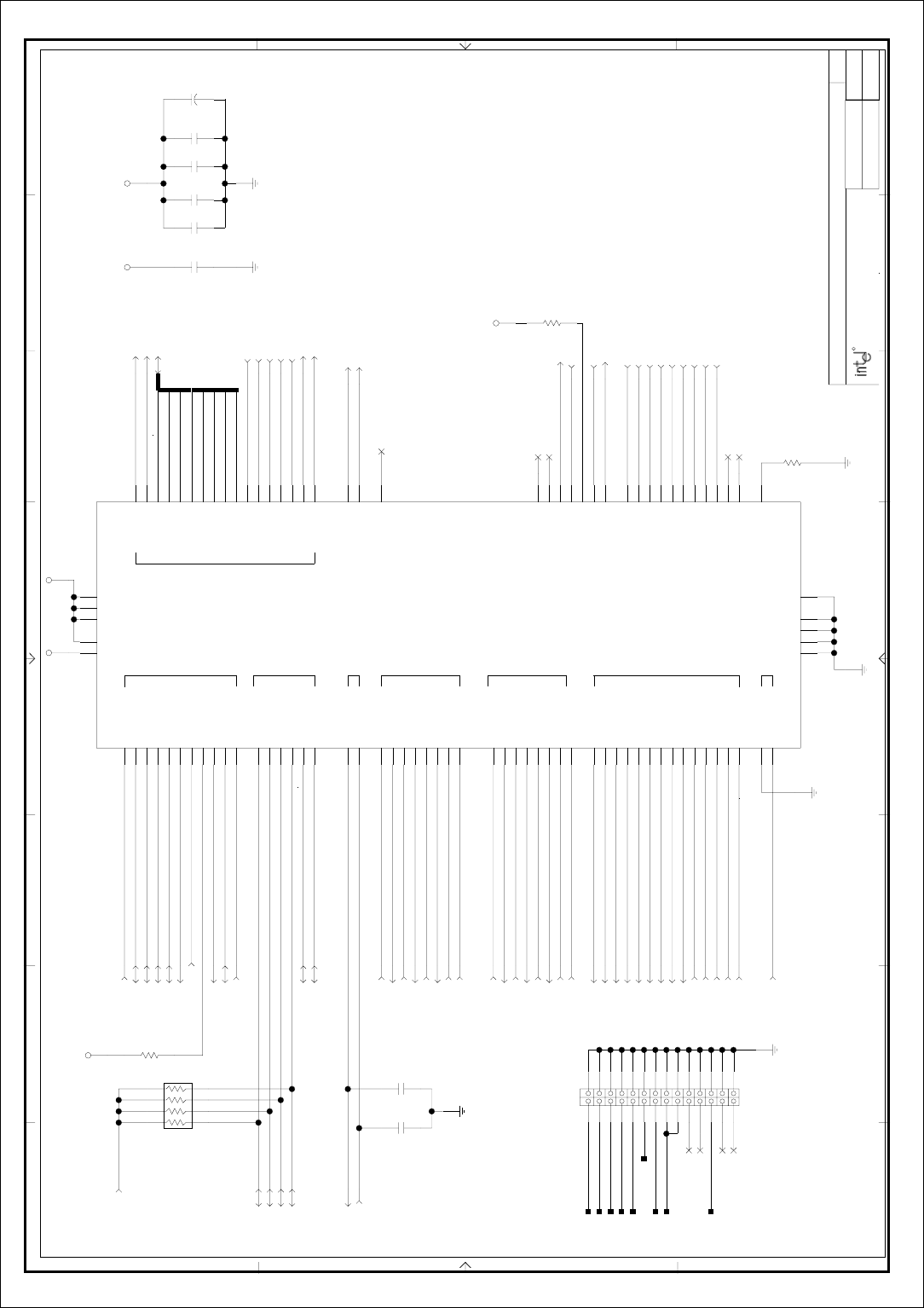

SUPER I/O

R313

4.7K

KBCLK

31

9

LPC_PME#

U17

27

18

45

44

15

11

10

93

65

53

96

85

14

83

9

67

77

30

95

84

98

87

92

90

16

17

78

75

74

73

72

71

70

69

6829

3

58

59

26

24

25

23

22

21

20

56

57

63

62

61

66

13

12

49

48

52

51

50

47

46

43

42

41

39

38

37

36

35

34

33

32

76

60

31

7

28

54

55

81

100

89

97

86

4

5

2

1

8

94

91

99

88

19

6

79

40

82

80

64

R312

4.7K

J20

2827

25 26

9

87

65

43

2423

2221

20

2

19

1817

1615

1413

1211

10

1

SIO_14MHZ

5

9,10,12

LAD3/FWH3

9,10,12

LAD1/FWH1

9,10,12

LAD0/FWH0

9,12

LDRQ#0

SIO_PCLK7

5,12

31

MDAT

MCLK

31

30

RXD0

30

TXD0

30

DSR#0

30

RTS#0

30

CTS#0

30

DTR#0

30

RI#0

30

DCD#0

30

RXD1

30

DSR#1

30

RTS#1

30

CTS#1

30

DTR#1

30

RI#1

30

DCD#1

31

MTR#0

31

DIR#

31

HDSEL#

31

INDEX#

31

TRK#0

29

SLIN#

31

RDATA#

29

PAR_INIT#

31

DSKCHG#

29

AFD#

29

STB#

29

SLCT

29

PE

29

BUSY

29

ACK#

29

ERR#

8,38

KBRST#

8,38

A20GATE

SERIRQ

8,12,26,38

23

PWM1

9

LPC_SMI#

32

MIDI_IN

32

MIDI_OUT

32

J1BUTTON1

32

J1BUTTON2

32

J2BUTTON1

32

J2BUTTON2

32

JOY1X

32

JOY1Y

32

JOY2X

32

JOY2Y

9,10,12

LAD2/FWH2

31

KBDAT

30

TXD1

23

TACH2

23

PWM2

31

DRVDEN#0

23

KEYLOCK#

31

DRVDEN#1

31

DS#0

31

STEP#

31

WDATA#

31

WGATE#

31

WRTPRT#

9,10,12 LAD3/FWH3

9,10,12 LAD2/FWH2

9,10,12 LAD1/FWH1

9,10,12 LAD0/FWH0

9,10,12 LFRAME#/FWH4

5,12

SIO_PCLK7

9,12

LDRQ#0

8,12,26,38 SERIRQ

PDR7

PDR0

PDR1

PDR2

PDR3

PDR4

PDR5

PDR6

29

PDR[7:0]

23

IRRX

23

IRTX

6,8,10,11,12,24,25,26,27

PCIRST#

LPCPD#

SYSOPT

9,10,12

LFRAME#/FWH4

470PF

C320

470PF

C317

0.1UF

C309

0.1UF

C321C348

0.1UF

C313

0.1UF 0.1UF

C323

2.2UF

C349

21

31 VCC5_KBMS_J

4.7K

R315

RP5

4.7K

1

2

3

45

6

7

8

CPU_TACH1

6,8,10,11,12,24,25,26,27

PCIRST#

DRAWN BY:

LAST REVISED: SHEET:

FOLSOM, CALIFORNIA 95630

1900 PRAIRIE CITY ROAD

87 6 54 32 1

A

B

C

D

12345678

D

C

B

A

PCG PLATFORM DESIGN

REV:

0.5

PROJECT:

OF 40

TITLE: INTEL(R) 820E CHIPSET 2 DIMM FCPGA REFERENCE BOARD

R

PCG AE Camino2

VCC3_3

SIO

LPC47B27X

A20GATE

ACK#

ALF#

AVSS

BUSY

CLKI32

CLOCKI

CTS1#

CTS2#

DCD1#

DCD2#

DIR#

DRVDEN0

DRVDEN1

DS0#

DSKCHG#

DSR1#

DSR2#

DTR1#

DTR2#

ERROR#

FAN1/GP33

FAN2/GP32

FDC_PP/DDRC/GP43

GND1

GND2

GND3

GND4

GP10/J1B1

GP11/J1B2

GP12/J2B1

GP13/J2B2

GP14/J1X

GP15/J1Y

GP16/J2X

GP17/J2Y

GP20/P17

GP21/P16

GP22/P12

GP25/MIDI_IN

GP26/MIDI_OUT

GP27/IO_SMI#

GP30/FAN_TACH2

GP31/FAN_TACH1

GP60/LED1

GP61/LED2

HDSEL#

INDEX#

INIT#

IRRX2/GP34

IRTX2/GP35

KBDRST

KCLK

KDAT

LAD0

LAD1

LAD2

LAD3

LDRQ#

LFRAME#

LRESET#

MCLK

MDAT

MTR0#

PCI_CLK PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PE

PME#

RDATA#

RI1#

RI2#

RTS1#

RTS2#

RXD1

RXD2_IRRX

SERIRQ

SLCT#

SLCTIN#

STEP#

STROBE#

TRK0#

TXD1

TXD2_IRTX

VCC1

VCC2

VCC3

WDATA#

WGATE#

WRTPRT#

VREF

GP24/SYSOPT

VTR

LPCPD#

SERIAL PORT 1

SERIAL PORT 2

FDC I/F

LPC I/F

INFRARED I/F

CLOCKS

KYBD/MSE I/F

PARALLEL PORT I/F

VCC3_3

VCC5

VCC5 VCC3_3

VCC3_3

+

Pulldown on SYSOPT for IO address of 0x02E

LPC header. For debug only.

Super I/O

Place decoupling caps near each power pin.Place next to VREF.