Intel

®

820E Chipset

R

40 Design Guide

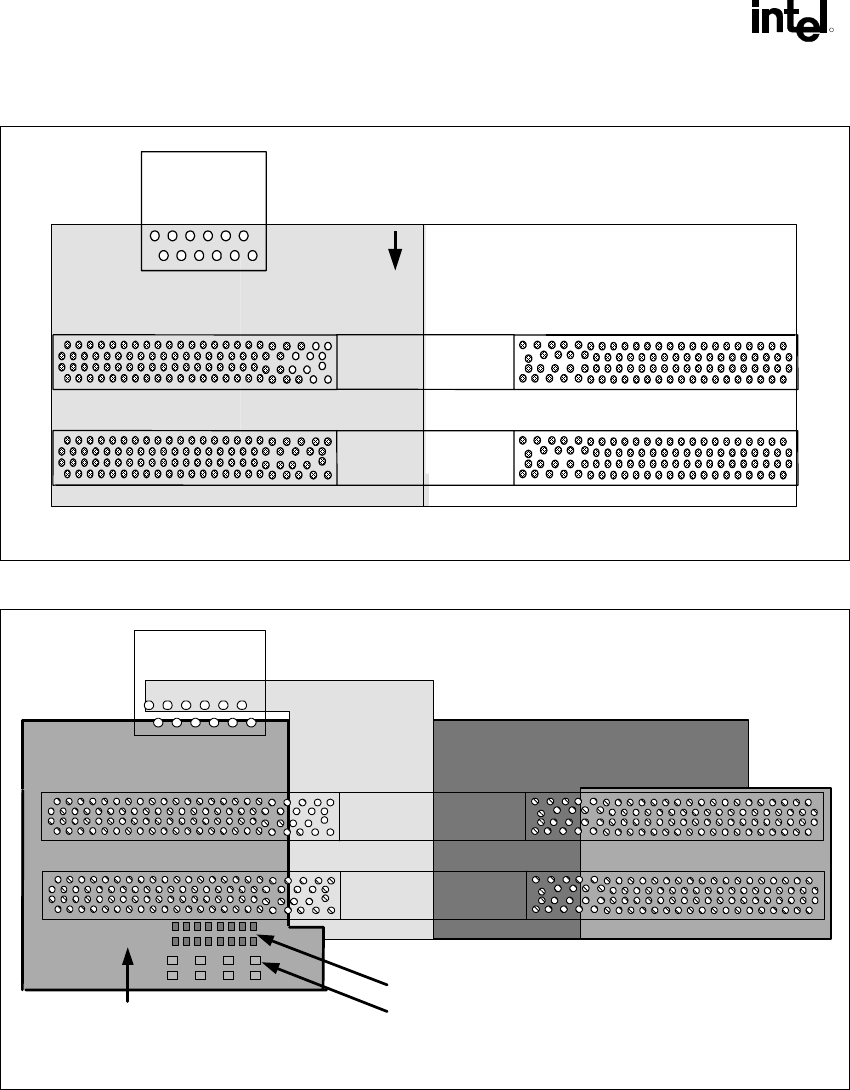

Figure 19. Incorrect Direct RDRAM* Ground Plane Referencing

3.3-V Plane

1.8-V Plane

MCH

Wrong

dir_Rambus_gnd_plane_ref_incorrect

RIMM2

RIMM1

Figure 20. Direct RDRAM* Ground Plane Reference

Extend GND plane

reference island beyond

V

TERM

capacitors

GND Plane

1.8-V Plane

RIMM1

GND PlaneGND Plane

MCH

Required

Vterm layer not shown

V

TERM

resistors

V

TERM

capacitors

dir_Rambus_gnd_plane_ref

RIMM2

3.3-V Plane

The ground reference island under the RSL signals MUST be connected to the ground pins on the RIMM

connector and the ground vias used to connect the ground isolation on the first and fourth layers.