Intel

®

820E Chipset

R

Design Guide 95

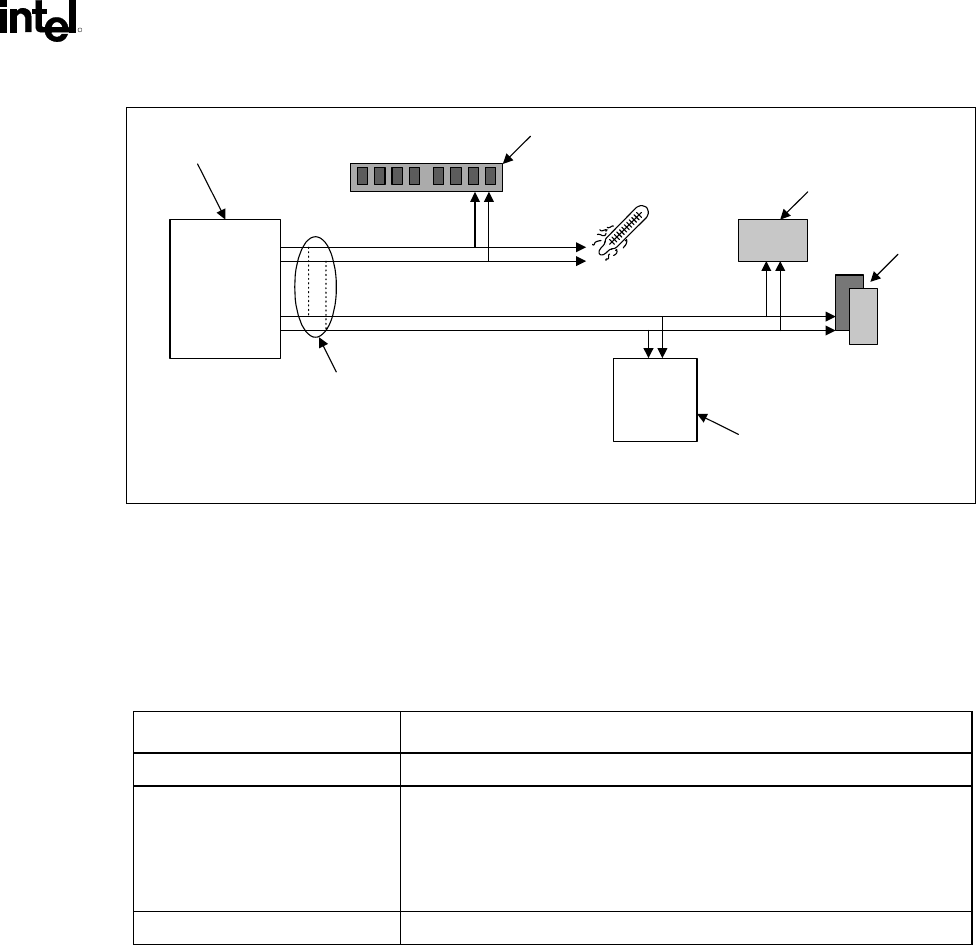

Figure 57. SMBUS/SMLink Interface

82801BA

ICH2

Host controller

slave interface

SMBus

SMBCLK

SPD data

Temperature on

thermal sensor

Network

interface

card on PCI

Microcontroller

Intel

®

8255

Motherboard

LAN controller

Wire OR

(optional)

SMLink0

SMLink1

SMLink

SMBDATA

smbus_smlink_IF

Note: Intel does not support external access to the ICH2’s integrated LAN controller via the SMLink interface.

Also, Intel does not support access to the ICH2’s SMBus slave interface by the ICH2’s SMBUS host

controller.

The following table describes the pull-up requirements for different implementations of the SMBus and

SMLink signals.

Table 20. Pull-Up Requirements for SMBus and SMLink Signals

SMBus / SMLink Use Implementation

Alert-on-LAN* signals 4.7 kΩ pull-up resistors to 3.3 V

SB

are required.

GPIOs Pull-up resistors to 3.3 V

SB

and the signals must be allowed.

To change states on power-up. (For example, during power-up the ICH2

will drive heartbeat messages until the BIOS programs these signals as

GPIOs.) The values of the pull-up resistors depend on the loading on the

GPIO signal.

Unused 4.7 kΩ pull-up resistors to 3.3 V

SB

are required.