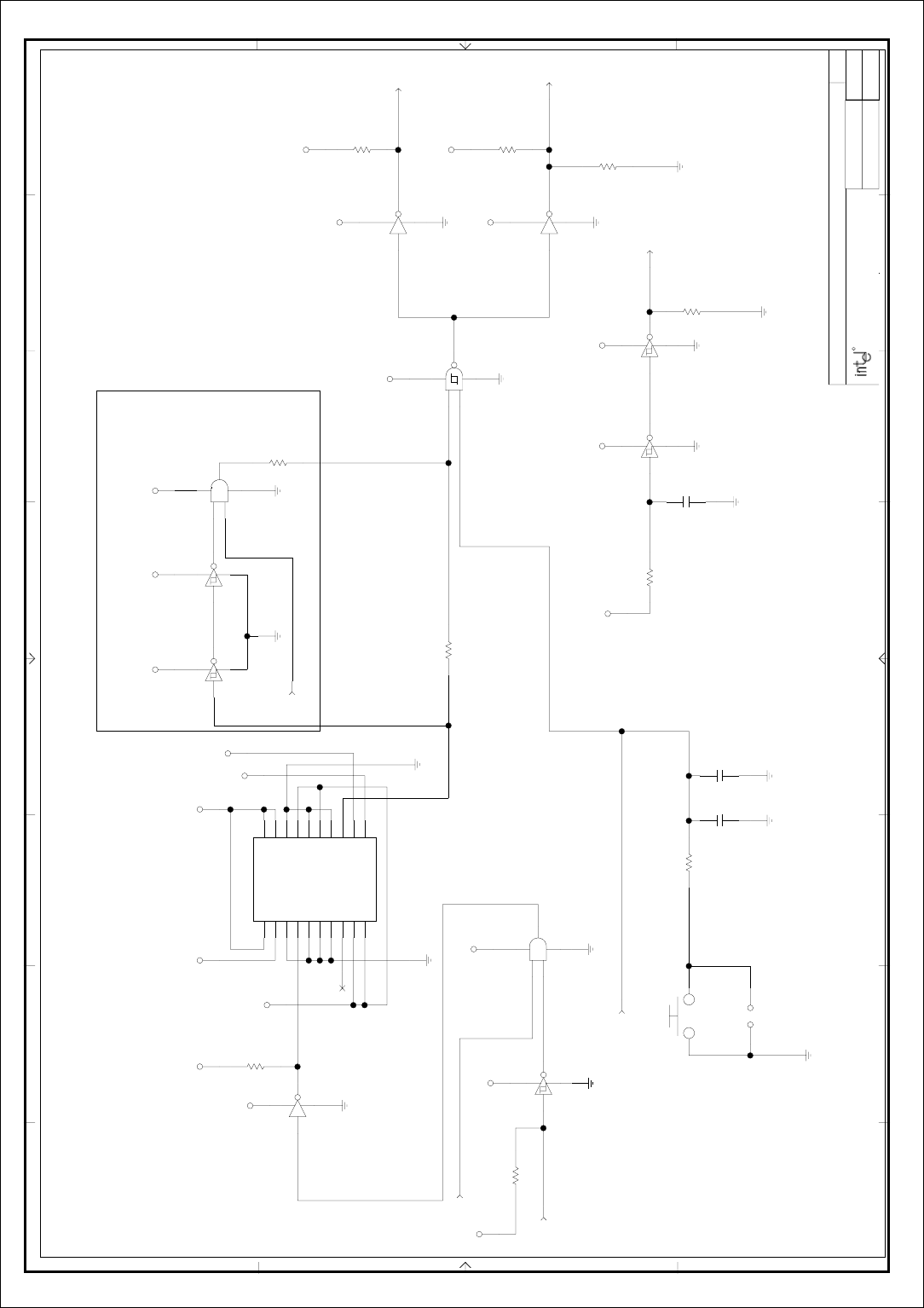

3-20-2000_10:15

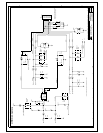

POWER CONNECTOR

36

10K

R536

VCOREDET

U3

14

7

11

12

13

RSTBTN_SW

U20

7

14

3 4 7,8,9,34PWROK

0K

R339

4.7K

R349

R342

0K

1M

R288

R251

22K

R347

4.7K

R343

22

U18

7

14

8

10

9

PWRGOOD

4,8

330

R96

1M

R348

J24

11

12

13

14

15

16

17

18

19

20

1

2

3

4

5

6

7

8

9

10

ATX_PWOK

POK_U1 POK_U2

POK_U3

RSMRST#

8,9

RSMRSTRSMRST_U

ATX_PWOK_R

PWROK_INV

U3

2

1

3

7

14

U15

34

7

14

U20

21

14

7

U15

14

7

65

U15

98

7

14

U20

65

14

7

4

DBRESET#

10UF

C328C335

0.01UF

1UF

C266

U15

14

7

21

SW2

JP12

U15

13 12

7

14

VCOREDET#

4

PS_ON#

PS_ON

4,8,9,33

VRM_PWRGD

8,9,34

SLP_S3#

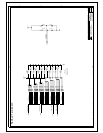

SN74LVC08A

DRAWN BY:

LAST REVISED: SHEET:

FOLSOM, CALIFORNIA 95630

1900 PRAIRIE CITY ROAD

87 6 54 32 1

A

B

C

D

12345678

D

C

B

A

PCG PLATFORM DESIGN

REV:

0.5

PROJECT:

OF 40

TITLE: INTEL(R) 820E CHIPSET 2 DIMM FCPGA REFERENCE BOARD

R

PCG AE Camino2

VCC3_3SBY

VCC3_3SBY

VCC3_3SBY

SN74LVC06A

GND

VCC

VCC3_3SBY

VCC3_3SBY

VCC3_3SBY VCC3_3SBY

VCC12-

VCC12

VCC5

VCC5SBY

VCC3_3

VCC5SBY

74LS132

VCC

GND

VCC2_5

VCC5SBY

ATX

3_3V11

-12V

GND13

PS_0N

GND15

GND16

GND17

-5V

5V19

5V20

3_3V1

3_3V2

GND3

5V4

GND5

5V6

GND7

PW_OK

5VSB

12V

VCC3_3SBY

SN74LVC08A

74LVC14A

SN74LVC06A

GND

VCC

VCC3_3SBY

74LVC14A 74LVC14A

VCC3_3SBY

SN74LVC06A

GND

VCC

74LVC14A

74LVC14A

VCC3_3SBY

VCC3_3SBY

VCC3_3SBY

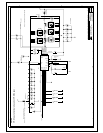

330 ohm pullup to VCC3_3 located on CPU sheet.

For test only

and Schmitt trigger logic.

using a 22 msec delay

Resume Reset circuitry

No stuff.

For test only

No stuff.

ATX Connector

Reset Button

74LVC14A has 5V input tolerance.

ITP Reset circuit. For debug only.

SN74LVC06A has 5V input tolerance.

SN74LVC06A has 5V output tolerance.

No stuff R342 when ITP is used.

Power Connector

220 ohm pullup to VCC3_3 is located on VRM sheet.