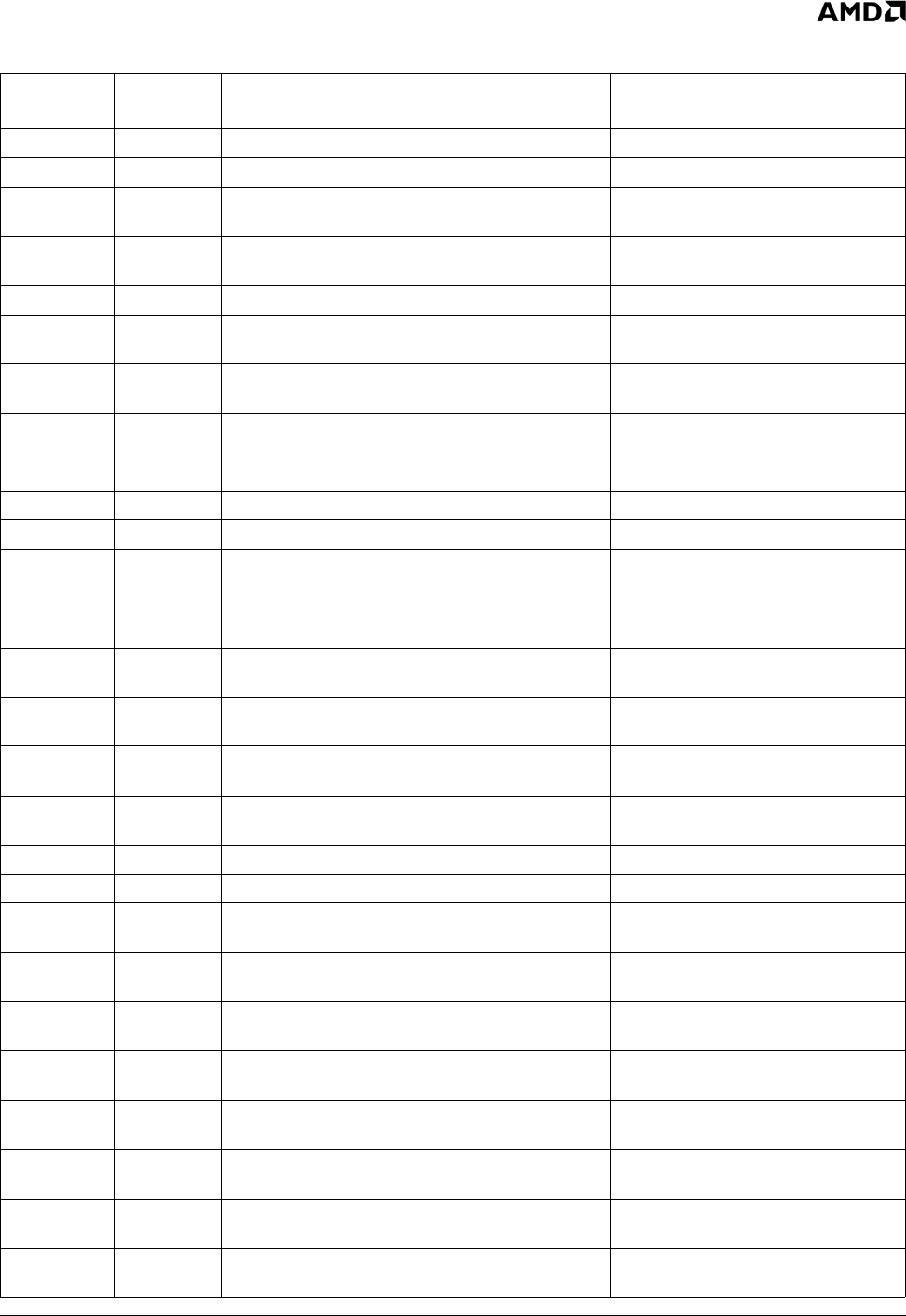

AMD Geode™ LX Processors Data Book 101

CPU Core Register Descriptions

33234H

00001335h R/W GS Segment Base/Limit MSR (GS_BASE_MSR) xxxxxxxx_xxxxxxxxh Page 134

00001336h R/W LDT Segment Base/Limit MSR (LDT_BASE_MSR) xxxxxxxx_xxxxxxxxh Page 134

00001337h R/W Temp Segment Base/Limit MSR

(TEMP_BASE_MSR)

xxxxxxxx_xxxxxxxxh Page 134

00001338h R/W TSS Segment Base/Limit MSR

(TSS_BASE_MSR)

xxxxxxxx_xxxxxxxxh Page 134

00001339h R/W IDT Segment Base/Limit MSR (IDT_BASE_MSR) xxxxxxxx_xxxxxxxxh Page 134

0000133Ah R/W GDT Segment Base/Limit MSR

(GDT_BASE_MSR)

xxxxxxxx_xxxxxxxxh Page 134

0000133Bh R/W SMM Segment Base/Limit MSR

(SMM_BASE_MSR

xxxxxxxx_xxxxxxxxh Page 134

0000133Ch R/W DMM Segment Base/ Limit MSR

(DMM_BASE_MSR)

xxxxxxxx_xxxxxxxxh Page 134

00001340h R/W Debug Registers 1 and 0 MSR (DR1_DR0_MSR) xxxxxxxx_xxxxxxxxh Page 135

00001341h R/W Debug Registers 3 and 2 MSR (DR3_DR2_MSR) xxxxxxxx_xxxxxxxxh Page 135

00001343h R/W Debug Registers 7 and 6 MSR (DR6_DR7_MSR) 00000000_FFFF0000h Page 136

00001350h R/W Extended Debug Registers 1 and 0 MSR

(XDR1_XDR0_MSR)

00000000_00000000h Page 137

00001351h R/W Extended Debug Registers 3 and 2 MSR

(XDR3_XDR2_MSR)

00000000_00000000h Page 137

00001352h R/W Extended Debug Registers 5 and 4 MSR

(XDR5_XDR4_MSR)

FFFFFFFF_00000000h Page 138

00001353h R/W Extended Debug Registers 7 and 6 MSR

(XDR7_XDR6_MSR)

xxxxxxxx_xxxxxxxxh Page 138

00001354h R/W Extended Debug Registers 9 and 8 MSR

(XDR9_XDR8_MSR)

FFFFFFFF_00000000h Page 140

00001355h R/W Extended Debug Registers 11 and 10 MSR

(XDR11_XDR10_MSR)

xxxxxxxx_xxxx0000h Page 141

00001360h R/W EX Stage Instruction Pointer MSR (EX_IP_MSR) 00000000_00000000h Page 141

00001361h R/W WB Stage Instruction Pointer MSR (WB_IP_MSR) 00000000_00000000h Page 142

00001364h RO EX Stage Linear Instruction Pointer MSR

(EX_LIP_MSR)

00000000_00000000h Page 142

00001365h RO WB Stage Linear Instruction Pointer MSR

(WB_LIP_MSR)

00000000_00000000h Page 143

00001366h RO C1/C0 Linear Instruction Pointer MSR

(C1_C0_LIP_MSR)

00000000_00000000h Page 143

00001367h RO C3/C2 Linear Instruction Pointer MSR

(C3_C2_LIP_MSR)

00000000_00000000h Page 144

00001370h R/W Floating Point Environment Code Segment

(FPENV_CS_MSR)

00000000_00000000h Page 144

00001371h R/W Floating Point Environment Instruction Pointer

(FPENV_IP_MSR)

00000000_00000000h Page 145

00001372h R/W Floating Point Environment Data Segment

(FPENV_DS_MSR)

00000000_00000000h Page 145

00001373h R/W Floating Point Environment Data Pointer

(FPENV_DP_MSR)

00000000_00000000h Page 146

Table 5-13. CPU Core Specific MSRs Summary (Continued)

MSR

Address Type Register Name Reset Value Reference