AMD Geode™ LX Processors Data Book 267

Graphics Processor Register Definitions

33234H

6.4.2.12 Vector Mode (GP_VECTOR_MODE)

Writing to this register configures the vector mode and initiates the rendering of the vector. If a BLT or vector operation is

already in progress when this register is written, the BLT pending bit in GP_BLT_STATUS (GP Memory Offset 44h)is set

and the vector is queued to begin when the current operation is complete. Software should not write to any register (other

than GP_HOST_SRC if required) while the BLT pending bit is set since it will corrupt the pending vector operation. Setting

the TH bit causes the vector operation to wait until the next VBLANK before beginning rendering. Software may still queue

another operation behind a throttled vector as long as the BLT pending bit is clear.

7:0 ROP/a

R

Raster Operations (ROP). Combination rule for source, pattern and destination when

performing raster operations. (See Section 6.3.10 "Raster Operations (ROP)" on page

251.)

Alpha Value (a

R

). Alpha value that can be used for some of the alpha compositing oper-

ations.

GP Memory Offset 3Ch

Typ e WO

Reset Value 00000000h

GP_RASTER_MODE Bit Descriptions (Continued)

Bit Name Description

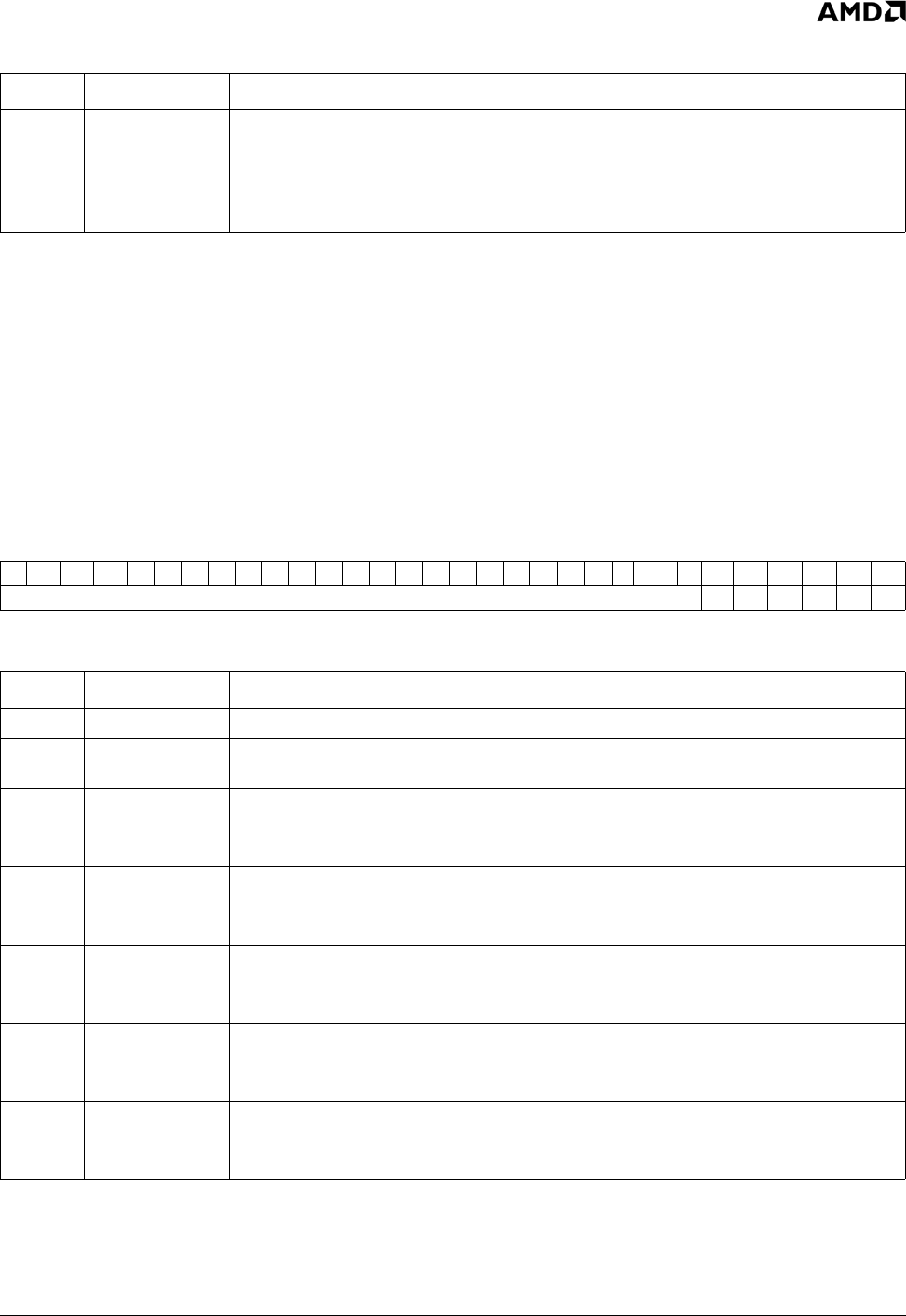

GP_VECTOR_MODE Register Map

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD CP TH DR DN DJ YJ

GP_VECTOR_MODE Bit Descriptions

Bit Name Description

31:6 RSVD Reserved. Write to 0.

5CP Checkpoint. Generates interrupt when this vector is completed if checkpoint interrupt is

enabled.

4TH Throttle.

0: Operation begins immediately.

1: Operation waits until next VBLANK before beginning.

3DR Destination Required.

0: Destination data is not needed for operation.

1: Destination data is needed from frame buffer.

2DN Minor Direction.

0: Negative minor axis step.

1: Positive minor axis step.

1DJ Major Direction.

0: Negative major axis step.

1: Positive major axis step

0YJ Y Major.

0: X major vector.

1: Y major vector.