336 AMD Geode™ LX Processors Data Book

Display Controller Register Descriptions

33234H

6.6.7.2 DC Palette Data (DC_PAL_DATA)

This register contains the data for a palette access cycle. When a read or write to the palette RAM occurs, the previous out-

put value is held for one additional Dot clock period. This effect should go unnoticed and will provide for sparkle-free

updates. Prior to a read or write to this register, the DC_PAL_ADDRESS register (DC Memory Offset 070h) should be

loaded with the appropriate address. The address automatically increments after each access to this register, so for

sequential access, the address register need only be loaded once.

If the SGRE bit in DC_GENERAL_CFG is set (DC Memory Offset 004h[25] = 1), this register reads back the state of the

graphics output pixel stream signature.

6.6.7.3 DC Display FIFO Diagnostic (DC_DFIFO_DIAG)

This register is provided to enable testability of the display FIFO RAM. Before it is accessed, the DIAG bit in the

DC_GENERAL_CFG register should be set high (DC Memory Offset 004h[28] = 1) and the DFLE bit should be set low (DC

Memory Offset 004h[0] = 0). In addition, the TGEN bit should be set low (DC Memory Offset 008h[0] = 0) and all clock gat-

ing should be disabled (MSR 80002004h = 0). Since each FIFO entry is 64 bits, an even number of write operations should

be performed. Each pair of write operations causes the FIFO write pointer to increment automatically. After all write opera-

tions are performed, a pair of reads of don't care data should be performed to load 64 bits of data into the output latch. Each

subsequent read contains the appropriate data that was previously written. Each pair of read operations causes the FIFO

read pointer to increment automatically.

This register is also used for writing to the compressed line buffer. Each pair of writes to this register stores a 64-bit data

value that is used for the next write to the compressed line buffer. The write pulse to the compressed line buffer is gener-

ated by writing dummy data to the DC_PAL_DATA register (DC Memory Offset 074h[23:0]) while in DIAG mode.

DC Memory Offset 074h

Typ e R /W

Reset Value xxxxxxxxh

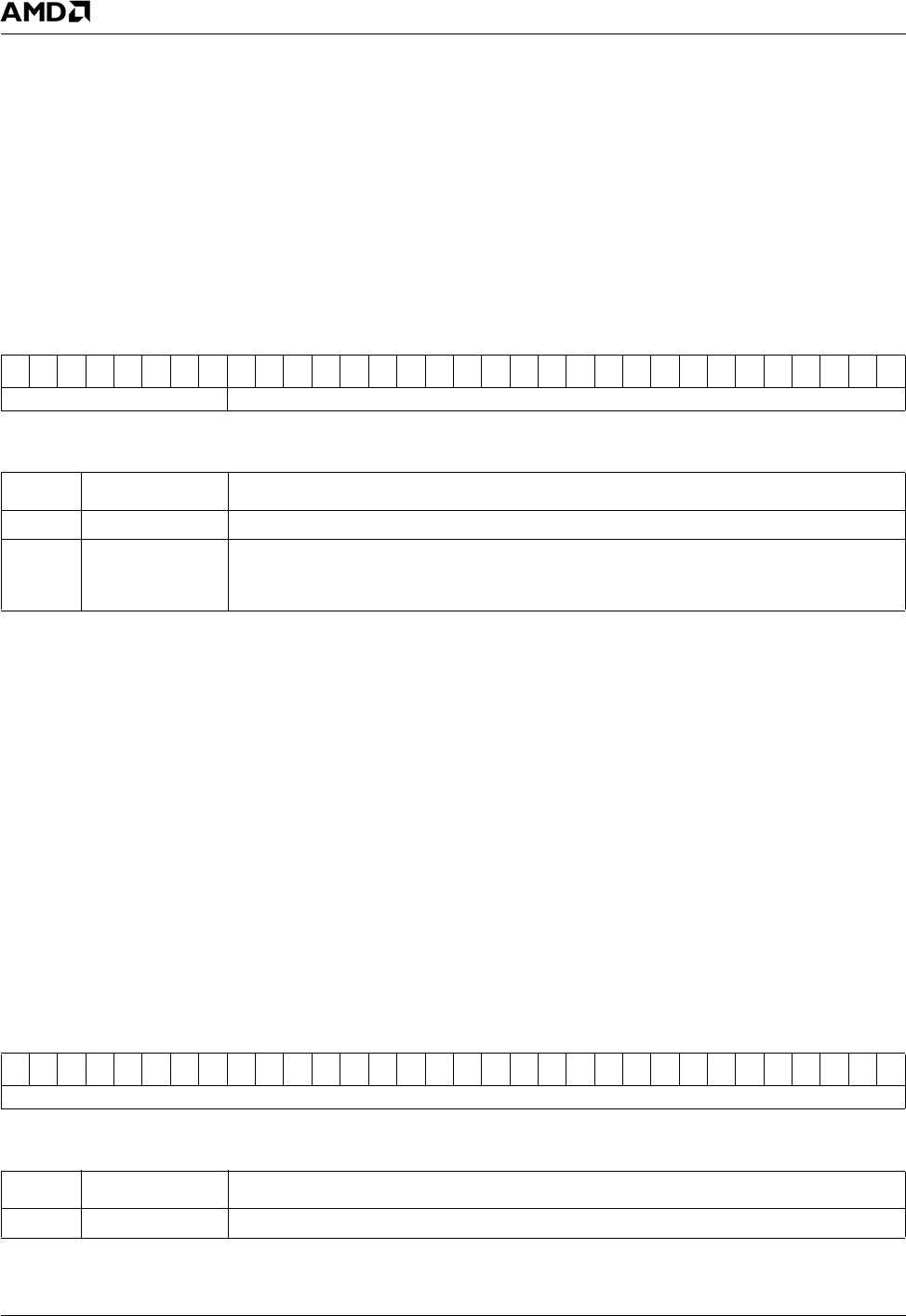

DC_PAL_DATA Register Map

313029282726252423222120191817161514131211109876543210

RSV D PA L_ DATA

DC_PAL_DATA Bit Descriptions

Bit Name Description

31:24 RSVD Reserved.

23:0 PAL_DATA PAL Data. This 24-bit field contains the read or write data for a palette access. If

DC_GENERAL_CFG[SGRE] (DC Memory Offset 004h[25]) is set, a read to this register

will read back the state of the graphics output pixel stream signature.

DC Memory Offset 078h

Typ e R /W

Reset Value xxxxxxxxh

DC_DFIFO_DIAG Register Map

313029282726252423222120191817161514131211109876543210

DFIFO_DATA

DC_DFIFO_DIAG Bit Descriptions

Bit Name Description

31:0 DFIFO_DATA Display FIFO Diagnostic Read or Write Data.