AMD Geode™ LX Processors Data Book 163

CPU Core Register Descriptions

33234H

5.5.2.65 Data Memory Subsystem Prefetch Lock MSR (DM_PFLOCK_MSR)

20 NOPFXEVCT No Prefetch Prefix Evictions. This bit disables clean line eviction in the case where a

new allocation occurs on a load/store miss when a move string operation uses the

REPNZ prefix instead of the normal REP prefix (restricted cache move feature, see PFX-

LOCK, bits [15:0]). When NOPFXEVCT is set, cache lines replaced by a load instruction

using the restricted cache prefix (REPNZ) will not be evicted if they are clean. (See EVC-

TONRPL bit description in DM_CONFIG0_MSR (MSR 00001800h[14]) for clean line

eviction feature). Clean line evictions of this type can be disabled in order to protect the

Victim mode L2 cache from being polluted by the transient data being moved. If this bit is

a 0, then normal clean line eviction occurs on any line replacement if enabled by the

EVCTONRPL bit. Note that any dirty line that is replaced will be evicted regardless of the

state of this bit. (Default = 0)

19:16 ARRAYDIS Array Disable. Mask used to disable individual cache arrays (way groups) in the DM to

save power or to avoid array defects. When an array is disabled, the DM will not read or

write the data array or tag array associated with this way group, reducing power. Any

data in the cache must be flushed before disabling an array or it will be lost.

Bit 19: Ways 15-12

Bit 18: Ways 11-8

Bit 17: Ways 7-4

Bit 16: Ways 3-0

0: Enable. (Default)

1: Disable.

15:0 PFXLOCK Prefetch Prefix Instructions Lock. Bit mask of ways that cannot be allocated or

replaced on a load miss when a move string operation uses the REPNZ prefix (instead of

the normal REP prefix). If all ways are locked, caching is effectively disabled, though the

cache will still be interrogated. Note that the REPNZ prefix has no effect on PREFETCH

instructions or writes to a write-allocate region that miss the cache and cause a write-

allocate. (Default = 0)

MSR Address 00001804h

Typ e R /W

Reset Value 00000000_00000000h

DM_CONFIG1_MSR Bit Descriptions (Continued)

Bits Name Description

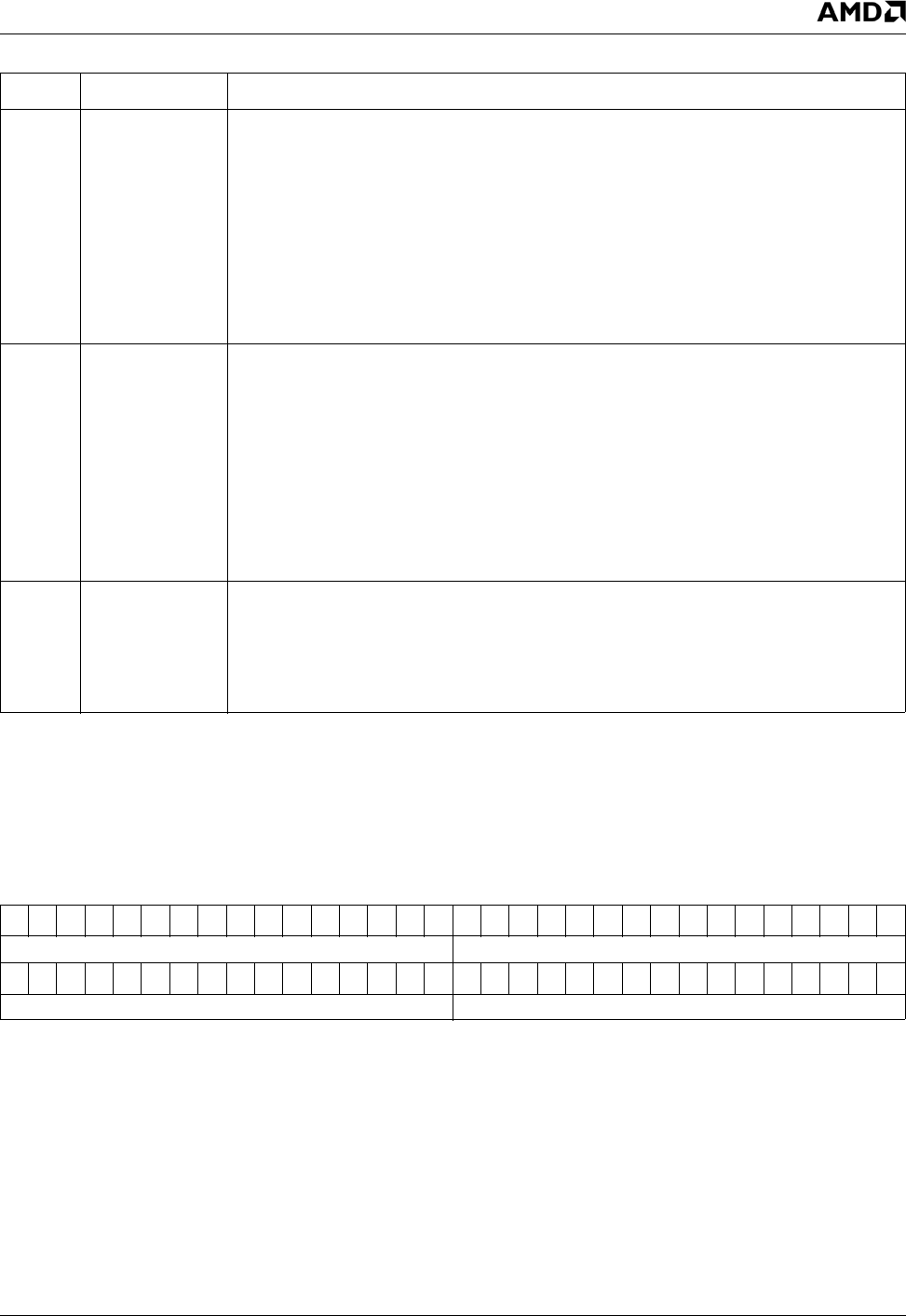

DM_PFLOCK_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

PFLOCKT2 PFLOCKT1

313029282726252423222120191817161514131211109876543210

PFLOCKT0 PFLOCKNTA