AMD Geode™ LX Processors Data Book 425

Video Processor Register Descriptions

33234H

6.8.3.4 Video Y Position (VY)

6.8.3.5 Video Scale (SCL)

VP Memory Offset 018h

Typ e R /W

Reset Value 00000000_00000000h

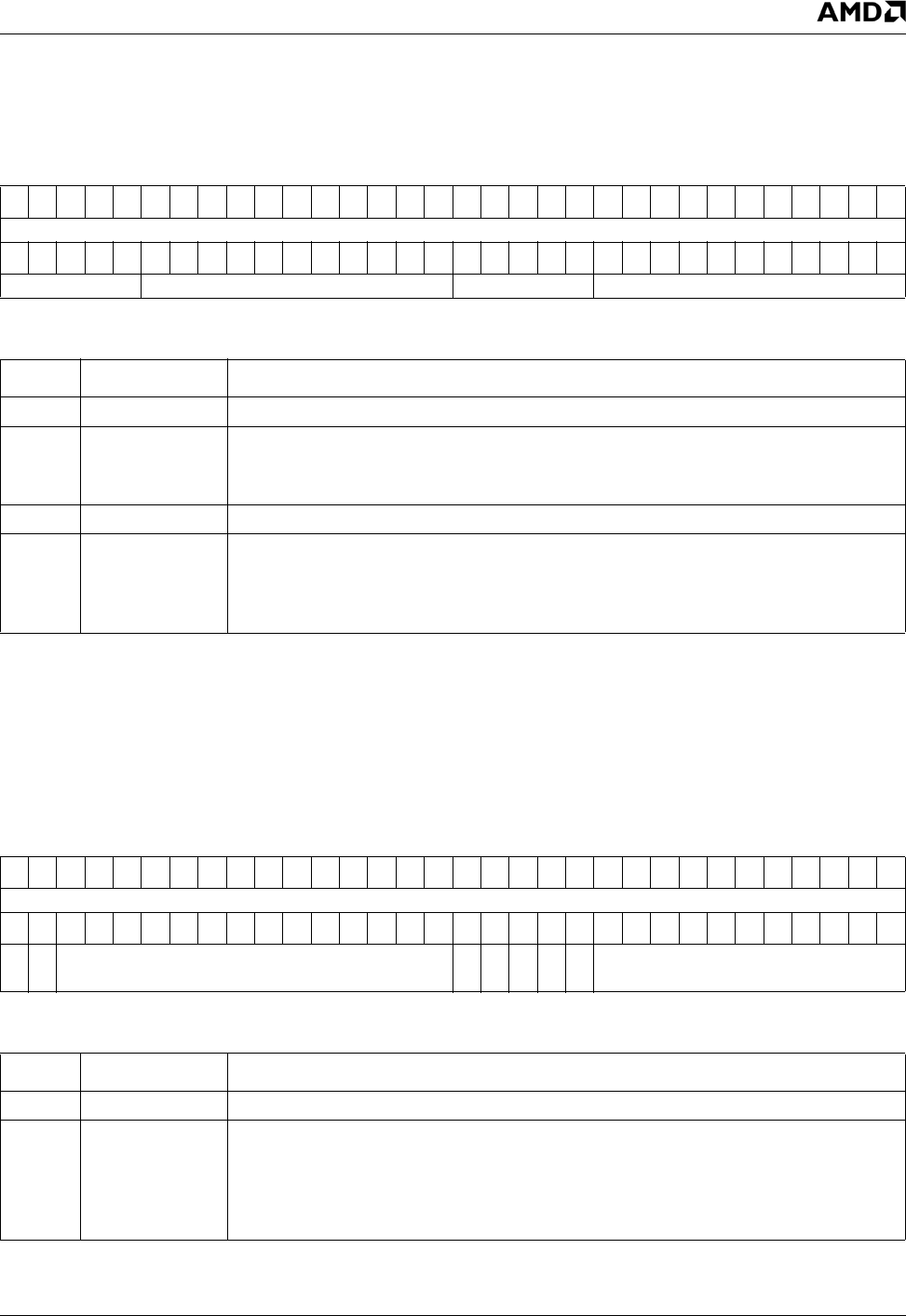

VY Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD VID_Y_END RSVD VID_Y_START

VY Bit Descriptions

Bit Name Description

63:27 RSVD (RO) Reserved (Read Only). Reads back as 0.

26:16 VID_Y_END Video Y End Position. Represents the vertical end position of the video window. This

value is calculated according to the following formula:

Value = Desired screen position + (V_TOTAL – V_SYNC_END) + 2. (Note 1)

15:11 RSVD (RO) Reserved (Read Only). Reads back as 0.

10:0 VID_Y_START Video Y Start Position. Represents the vertical start position of the video window. This

register is programmed relative to CRT Vertical sync input (not the physical screen posi-

tion). This value is calculated according to the following formula:

Value = Desired screen position + (V_TOTAL – V_SYNC_END) + 1. (Note 1)

Note 1. V_TOTAL and V_SYNC_END are the values written in the Display Controller module registers.

VP Memory Offset 020h

Typ e R /W

Reset Value 00000000_00000000h

SCL Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

GP

GB

RSVD

SP

DHD

COED

LPS

SP

VSL

SCL Bit Descriptions

Bit Name Description

63:32 RSVD (RO) Reserved (Read Only). Reads back as 0.

31 GP (RO) GLIU Passed (Read Only). This bit set indicates the GLIU line buffer fill has been

passed by the Dot display. Screen display tearing might occur. This bit clears on read.

This bit is typically set if during vertical downscale, the 2nd line buffer fill hasn’t started

before the Dot display has started. This indicates an error in that the GLIU line buffer fill

can’t keep up with the Dot clock display rate.