AMD Geode™ LX Processors Data Book 419

Video Processor Register Descriptions

33234H

6.8.2 Video Processor Module Specific MSRs

6.8.2.1 VP Diagnostic MSR (MSR_DIAG_VP)

MSR Address 48002010h

Typ e R /W

Reset Value 00000000_00000000h

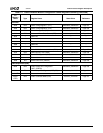

MSR_DIAG_VP Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

CM

NDM

SM DVAL D TSEL SP

MSR_DIAG_VP Bit Descriptions

Bit Name Description

63:32 RSVD Reserved.

31 CM 32-Bit CRC Mode. Selects 32-bit CRC generation.

0: Disable.

1: Enable.

30 NDM New Dither Mode. Selects either the legacy dither mode, or new dither mode.

The legacy dither mode has an errata with the first pixel. The new dither mode fixes this

errata. This bit provided for backward compatibility.

0: Legacy dither mode.

1: New dither mode.

29:28 SM Sim Mode. This field is used to put the VP in modes to aid verification.

00: Normal operation.

01: Graphics input bypasses VP and goes directly to FP.

10: Reserved.

11: Reserved.

27:20 DVAL DAC Test Value. 8-bit data value to drive to CRT DAC when selected by bit 19. Dupli-

cate copies of DAC Test Value are driven on DAC RGB.

crt_dac_r[7:0] = DAC Test Value[7:0] ([27:20] is this register)

crt_dac_g[7:0] = DAC Test Value[7:0] ([27:20] is this register)

crt_dac_b[7:0] = DAC Test Value[7:0] ([27:20] is this register)

To enable DAC Test Value to be driven to CRT DAC:

(DAC Test Value Select must = 0) AND

((VTM[6] = 0 AND MBD_MSR_DIAG[18:16] = 101h) OR

(VTM[6] = 1 AND VTM[3:0] = 0001h)

19 D DAC Test Value Select. Selects which data stream is sent to CRT DAC during CRT

DAC test mode.

0: 24-bit data to CRT DAC = {3{DAC Test Value[27:20]}} (3 time repeated 8-bit value).

1: 24-bit data to CRT DAC = gfx_data[23:0] (raw input from Display Controller).

18:16 RSVD Reserved. Reserved for test purposes. Set to 000 for normal operation.

15:0 SP Spares. Read/write, no function.