246 AMD Geode™ LX Processors Data Book

Graphics Processor

33234H

6.3.4 Vector Operation

Generating a vector requires a similar setup to a BLT. Reg-

isters must be written to specify the X and Y offsets of the

starting position of the vector within the frame buffer, the

vector length, and the three error terms required by the

Bresenham algorithm. In addition, any pattern colors and

pattern data should be loaded before initiating the vector.

Source data is not fetched when rendering vectors.

Instead, the contents of the GP_SRC_COLOR_FG register

(GP Memory Offset 10h) are used as the constant color for

the vector.

Vectors are initiated by writing to the GP_VECTOR_MODE

(GP Memory Offset 3Ch) register. This register also indi-

cates the need for destination data, and defines the major

axis (X or Y) and the major and minor directions (incre-

menting or decrementing) of the vector.

As in the BLT operation, vectors can be throttled by video

timing to prevent tearing. Setting the TH bit in the

GP_VECTOR_MODE register (GP Memory Offset 3Ch[4])

causes the Graphics Processor to wait until the next time

that video timing enters VBLANK before beginning to ren-

der the vector.

6.3.5 Pipelined Operation

Most of the graphics registers are pipelined. When the reg-

isters are programmed and the operation begins, the con-

tents of the registers are moved from slave registers to

master registers, leaving the slave registers available for

another operation. A second BLT or vector operation can

then be loaded into the slave registers while the first opera-

tion is rendered. If a second BLT is pending in the slave

registers, additional write operations to the graphics regis-

ters will corrupt the register values of the pending BLT.

Software must prevent this from happening by checking

the Primitive Pending bit in the GP_BLT_STATUS register

(GP Memory Offset 44h[2]).

The GP_PAT_COLOR_2 through GP_PAT_COLOR_5

(GP Memory Offset 20h-2Ch) registers are not pipelined. If

they are used in a new graphics operation, they should not

be written when the Primitive Busy bit (GP Memory Offset

44h[0]) is set and the Primitive Pending bit is not set in the

GP_BLT_STATUS register, and the active operation is

using these registers. Writing to these registers when a

BLT is active corrupts that operation.

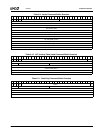

6.3.6 Pattern Generation

The Graphics Processor contains hardware support for 8x8

monochrome patterns (expanded to two colors), and color

patterns. Color patterns can be 8x4 in 8-bpp mode, 8x2 in

16-bpp mode, and 8x1 in 32-bpp mode. Pattern alignment

is based on the destination X and Y LSBs of the pixel being

drawn, so software can perform pattern justifications by

adjusting these two parameters. For solid fill primitives, the

pattern hardware is disabled and the pattern color is

always sourced from the GP_PAT_COLOR_0 register (GP

Memory Offset 18h).

6.3.6.1 Monochrome Patterns

Monochrome patterns are enabled by selecting mono-

chrome pattern mode in the GP_RASTER_MODE register

(GP Memory Offset 38h). Pixels that correspond to a clear

bit in the pattern are rendered using the color specified in

the GP_PAT_COLOR_0 (GP Memory Offset 18h) register,

and pixels that correspond to a set bit in the pattern are

rendered using the color specified in the

GP_PAT_COLOR_1 register (GP Memory Offset 1Ch).

If the pattern transparency bit is set in the

GP_RASTER_MODE register (GP Memory Offset 38h),

those pixels corresponding to a clear bit in the pattern data

are not drawn, leaving the frame buffer pixels at these loca-

tions untouched.

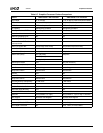

The pattern itself is loaded into the GP_PAT_DATA_0 and

GP_PAT_DATA_1 registers, with row 0 loaded into

GP_PAT_DATA_0 (GP Memory Offset 30h[7:0] (bit 7

being the left-most pixel on the screen)), and row 7 loaded

into GP_PAT_DATA_1 (GP Memory Offset 34h[31:24], see

Table 6-16).