110 AMD Geode™ LX Processors Data Book

CPU Core Register Descriptions

33234H

5.5.2 CPU Core Specific MSRs

5.5.2.1 Time Stamp Counter MSR (TSC_MSR)

5.5.2.2 Performance Event Counter 0 MSR (PERF_CNT0_MSR)

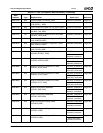

MSR Address 00000010h

Typ e R /W

Reset Value 00000000_00000000h

TSC_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

TSC (High DWORD)

313029282726252423222120191817161514131211109876543210

TSC (Low DWORD)

TSC_MSR Bit Descriptions

Bit Name Description

63:0 TSC Time Stamp Counter. This register is the 64-bit time stamp counter, also readable via

the RDTSC instruction.

Bus Controller Configuration 0 Register (MSR 00001900h) contains configuration bits

that determine if TSC counts during SMM, DMM, or Suspend modes.

Writes to this register clears the upper DWORD to 0. The lower DWORD is written nor-

mally.

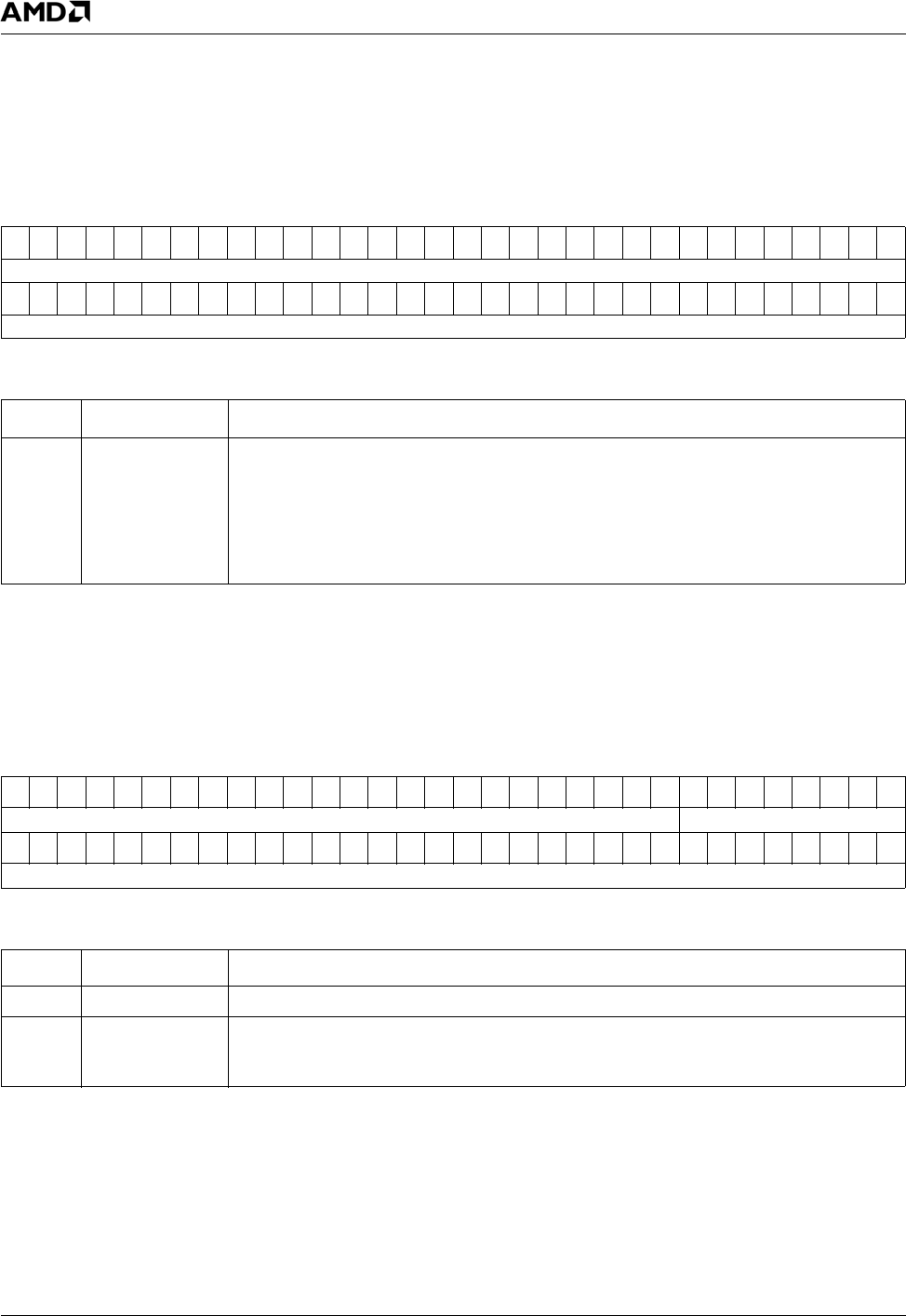

MSR Address 000000C1h

Typ e R /W

Reset Value 00000000_00000000h

PERF_CNT0_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD PERF_CNT0 (High Byte)

313029282726252423222120191817161514131211109876543210

PERF_CNT0 (Low DWORD)

PERF_CNT0_MSR Bit Descriptions

Bit Name Description

63:40 RSVD Reserved. Write as read.

39:0 PERF_CNT0 Performance Event Counter 0. This register is a 40-bit event counter used to count

events or conditions inside of the CPU Core. This counter is controlled by Performance

Event Counter 0 Select MSR (MSR 00000186h).