320 AMD Geode™ LX Processors Data Book

Display Controller Register Descriptions

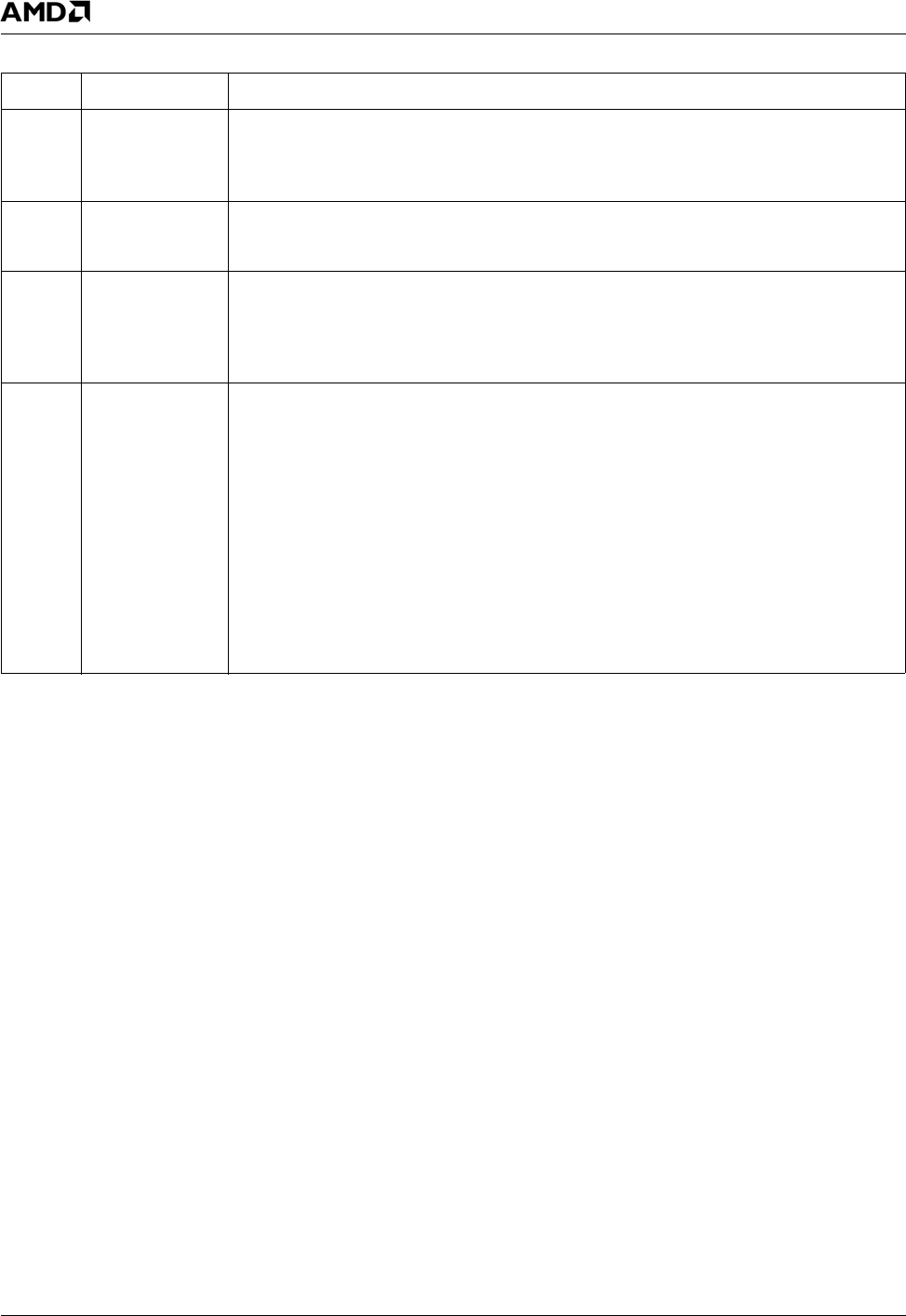

33234H

3 HPEN_2LB_INV High Priority Enable when Any Two Line Buffers Invalid. This bit enables the DC to

arbitrate at high priority if the scaler filter is enabled and any two of the three line buffers

that feed this filter are invalid. (The state of this bit is ignored if the scaler filter is dis-

abled.)

2 HPEN_3LB_INV High Priority Enable when Any Three Line Buffers Invalid. This bit enables the DC to

arbitrate at high priority if the scaler filter is enabled and all of the three line buffers that

feed this filter are invalid. (The state of this bit is ignored if the scaler filter is disabled.)

1 HPEN_LB_FILL High Priority Enable when Line Buffer Fill in Progress. This bit enables the DC to

maintain high priority requests whenever it is in the process of filling a line buffer. The line

buffer fill requires an entire scan line of data to be read from the data FIFO without inter-

ruption. Because the FIFO typically does not contain a full scan line of data, it is neces-

sary to fetch additional data from memory during this process.

0 LPEN_VSYNC Low Priority Enable at VSYNC. When this bit is set, the DC is forced to arbitrate at low

priority for a number of lines after the start of VSYNC. (This number of lines is pro-

grammed in bits [15:9] (LPEN_END_COUNT)) Because the line buffers, flicker filter buff-

ers, sync buffer, and data FIFO are all cleared at VSYNC, this mechanism prevents the

DC from spending an inordinate amount of time in high priority while filling all of these

buffers.

In most cases this value should be set three or four lines less than the distance between

VSYNC start and V_TOTAL This value may need to be lowered if VBI data is enabled.

During this low priority period after VSYNC, this mechanism overrides the watermark

mechanism for the data FIFO and all of the other mechanisms in this register except the

high priority enable when line buffer fill in progress mechanism enabled in bit 1

(HPEN_LB_FILL). Outside of this period, this mechanism has no effect on the priority

level of outgoing DC requests on the GLIU.

DC_ARB_CFG Bit Descriptions (Continued)

Bit Name Description