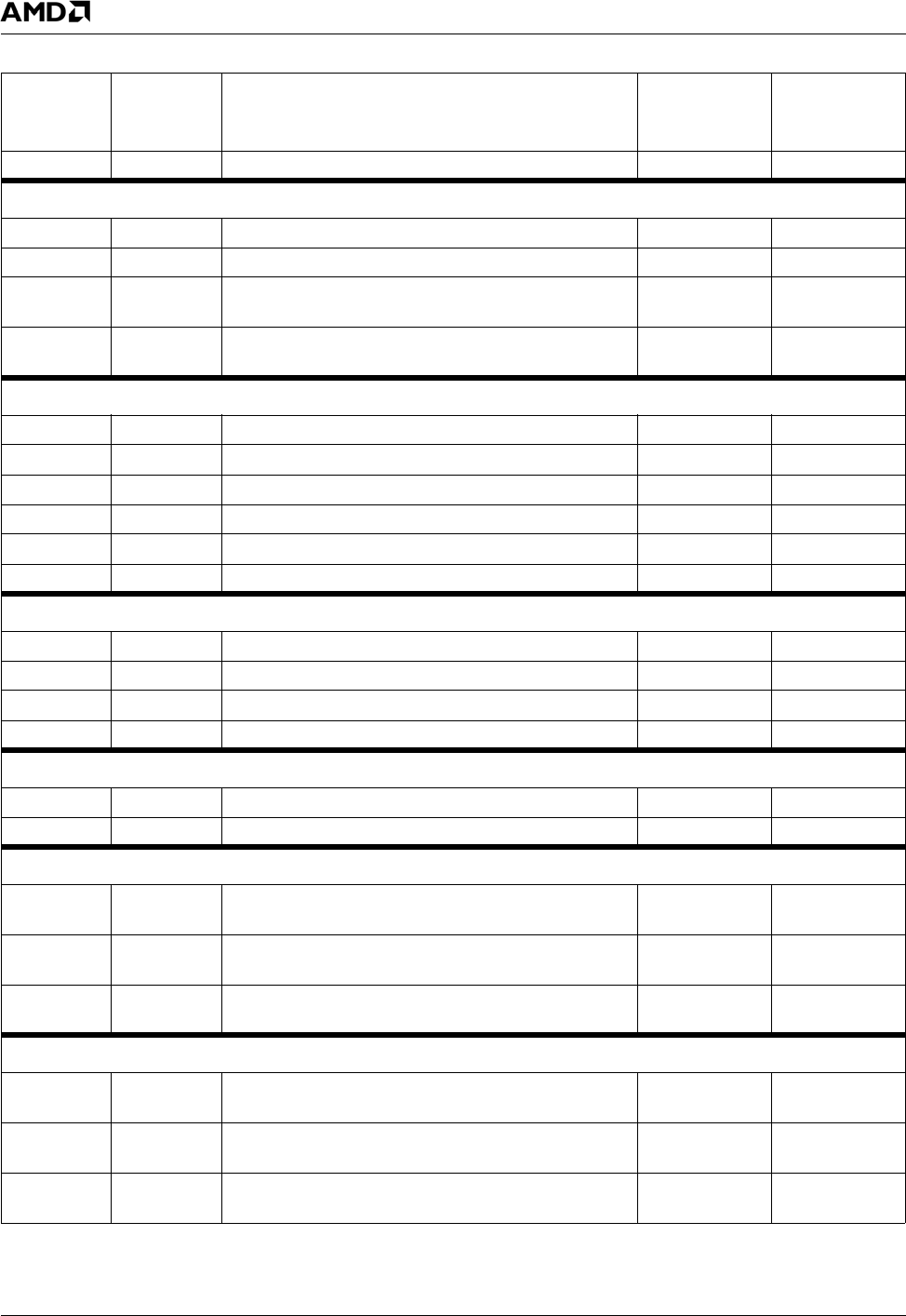

302 AMD Geode™ LX Processors Data Book

Display Controller Register Descriptions

33234H

08Ch R/W DC Dirty/Valid RAM Access (DC_DV_ACCESS) 0000000xh Page 340

Graphics Scaling Control Registers

090h R/W DC Graphics Filter Scale (DC_GFX_SCALE) 40004000h Page 341

094h R/W DC IRQ/Filter Control (DC_IRQ_FILT_CTL) 00000000h Page 342

098h R/W DC Filter Coefficient Data Register 1

(DC_FILT_COEFF1)

xxxxxxxxh Page 343

09Ch R/W DC Filter Coefficient Data Register 2

(DC_FILT_COEFF2)

xxxxxxxxh Page 344

VBI Control Registers

0A0h R/W DC VBI Even Control (DC_VBI_EVEN_CTL) xxxxxxxxh Page 344

0A4h R/W DC VBI Odd Control (DC_VBI_ODD_CTL) xxxxxxxxh Page 345

0A8h R/W DC VBI Horizontal Control (DC_VBI_HOR) xxxxxxxxh Page 345

0ACh R/W DC VBI Odd Line Enable (DC_VBI_LN_ODD) xxxxxxxxh Page 346

0B0h R/W DC VBI Even Line Enable (DC_VBI_LN_EVEN) xxxxxxxxh Page 346

0B4h R/W DC VBI Pitch and Size (DC_VBI_PITCH) xxxxxxxxh Page 347

Color Key Control Registers

0B8h R/W DC Color Key (DC_CLR_KEY) 00000000h Page 347

0BCh R/W DC Color Key Mask (DC_CLR_KEY_MASK) 00xxxxxxh Page 348

0C0h R/W DC Color Key Horizontal Position (DC_CLR_KEY_X) 00000000h Page 348

0C4h R/W DC Color Key Vertical Position (DC_CLR_KEY_Y) 00000000h Page 348

Interrupt and GenLock Registers

0C8h R/W DC Interrupt (DC_IRQ) 00000003h Page 349

0D4h R/W DC GenLock Control (DC_GENLK_CTL) xxxxxxxxh Page 350

Even Field Video Address Registers

0D8h R/W DC Even Field Video Y Start Address Offset

(DC_VID_EVEN_Y_ST_OFFSET)

xxxxxxxxh Page 351

0DCh R/W DC Even Field Video U Start Address Offset

(DC_VID_EVEN_U_ST_OFFSET)

xxxxxxxxh Page 352

0E0h R/W DC Even Field Video V Start Address Offset

(DC_VID_EVEN_V_ST_OFFSET)

xxxxxxxxh Page 352

Even Field Vertical Timing Registers

0E4h R/W DC Vertical and Total Timing for Even Fields

(DC_V_ACTIVE_EVEN_TIMING)

xxxxxxxxh Page 353

0E8h R/W DC CRT Vertical Blank Timing for Even Fields

(DC_V_BLANK_EVEN_TIMING)

xxxxxxxxh Page 354

0ECh R/W DC CRT Vertical Sync Timing for Even Fields

(DC_V_SYNC_EVEN_TIMING)

xxxxxxxxh Page 354

Table 6-47. DC Configuration Control Register Summary (Continued)

DC

Memory

Offset Type Register Name Reset Value Reference