AMD Geode™ LX Processors Data Book 25

Signal Definitions

33234H

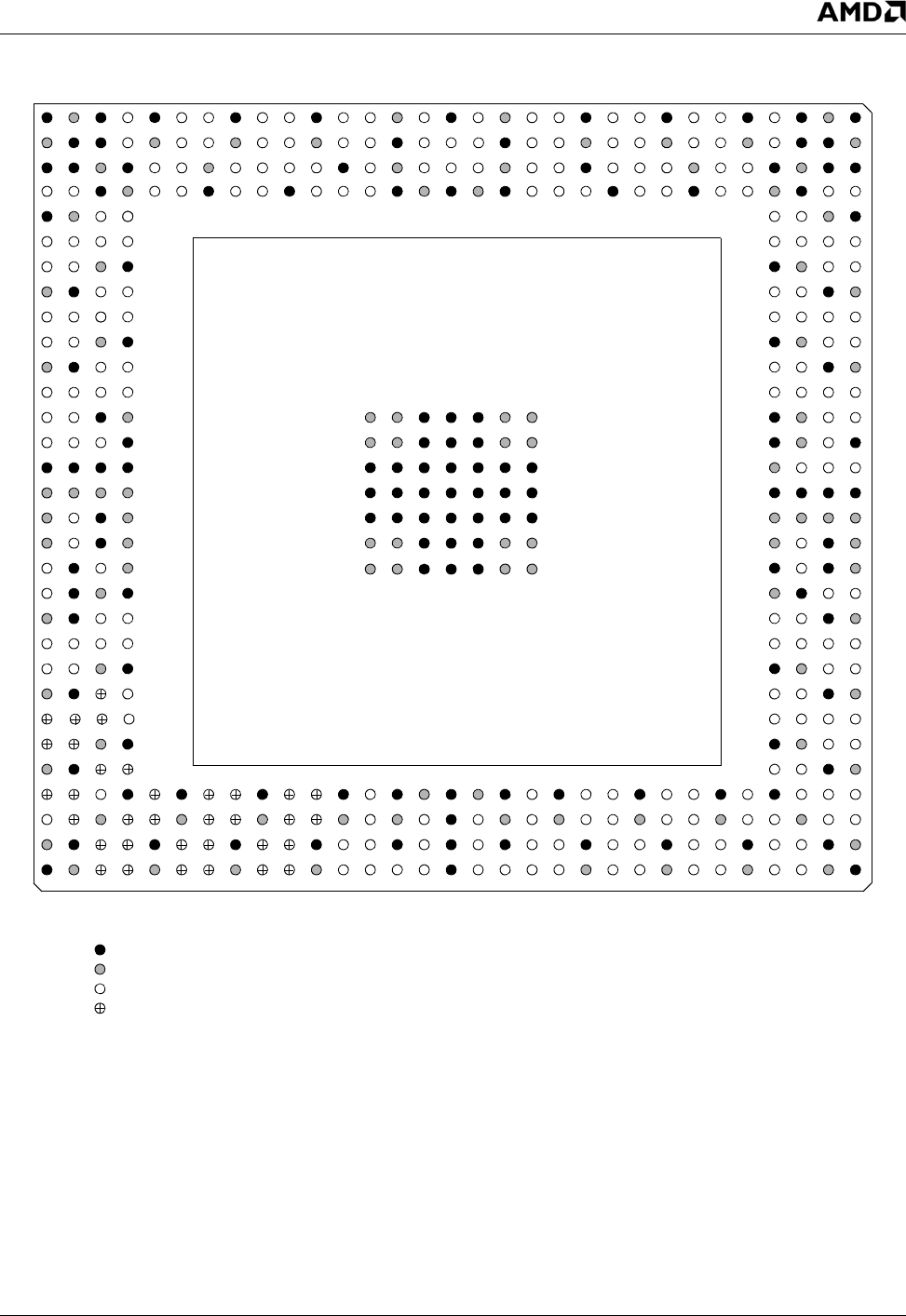

Figure 3-2. BGU481 Ball Assignment Diagram

12345678910111213141516171819202122232425262728293031

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

AG

AH

AJ

AK

AL

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

AG

AH

AJ

AK

AL

Note: Signal names have been abbreviated in this figure due to space constraints.

V

SS

V

MEM

V

SS

DQ21 V

SS

DQM2 DQ22 V

SS

DQ28 DQS3 V

SS

DQ26 DQ31 V

MEM

DQ32 V

SS

DQ37 V

MEM

DQM4 DQ39 V

SS

DQ40 DQ41 V

SS

DQ42 DQ43 V

SS

WE1# V

SS

V

MEM

V

SS

12345678910111213141516171819202122232425262728293031

V

MEM

V

SS

V

SS

DQ17 V

MEM

DQ18 DQ23 V

MEM

DQ24 DQM3 V

MEM

DQ27 TLA1 V

SS

TLA0 DQ36 DQ33 V

SS

DQ34 DQ38 V

MEM

DQ35 DQS5 V

MEM

DQ46 DQ47 V

MEM

CS0# V

SS

V

SS

V

MEM

V

SS

V

SS

V

MEM

V

SS

MA12 DQS2 V

MEM

DQ19 DQ29 DQ25 DQ30 V

SS

MA3 V

MEM

MA2 MA0 MA1 V

MEM

DQS4 BA1 V

SS

DQ44 DQ45 DQM5 V

MEM

RAS0# WE0# V

SS

V

MEM

V

SS

V

SS

DQ20 DQ16 V

SS

V

MEM

MA11 MA9 V

SS

MA7 MA8 V

SS

MA5 MA6 MA4 V

SS

V

CORE

V

SS

V

CORE

V

SS

MA10 SDK5P SDK5N V

SS

SDK4P SDK4N V

SS

BA0 RAS1# V

MEM

V

SS

CS3# DQ48

V

SS

V

MEM

DQ11 CKE0 CAS0# CAS1# V

MEM

V

SS

DQ15 DQ14 DQ10 CKE1

CS1# CS2# MA13 DQ49

DQ13 DQM1 V

MEM

V

SS

V

SS

V

MEM

DQ52 DQ53

V

MEM

V

SS

DQS1 SDK1N

SDK3N DQM6 V

SS

V

MEM

DQ9 DQ8 DQ12 SDK1P

SDK3P DQS6 DQ55 DQ54

DQ7 DQ3 V

MEM

V

SS

V

SS

V

MEM

DQ50 DQ51

V

MEM

V

SS

DQ6 SDK0N

SDK2N DQ60 V

SS

V

MEM

DQM0 DQS0 DQ2 SDK0P

SDK2P DQ61 DQ57 DQ56

DQ5 DQ1 V

SS

V

MEM

MVREF DQ0 DQ4 V

SS

V

SS

V

MEM

DQM7 DQS7

V

SS

V

MEM

DQ62 V

SS

V

SS

V

SS

V

SS

V

SS

V

CORE

V

CORE

V

CORE

V

CORE

DAV

DD

BLUE DAV

SS

V

CORE

DAV

DD

GREEN DAV

SS

DAV

DD

DVREF DAV

SS

RED DAV

DD

DRSET DAV

SS

V

IO

V

SS

VAV

DD

VAV

SS

VLPF TMS

DOTREF TDBGI TDI TDBGO

TDO TCLK V

IO

V

SS

V

IO

V

SS

VSYNC LDEMOD

DOTCLK VDEN HSYNC DISPEN

DRB17 DRB16 V

IO

V

SS

V

IO

V

SS

DRB18 DRB19

V

CORE

DQ63 DQ58 DQ59

V

SS

V

SS

V

SS

V

SS

V

CORE

V

CORE

V

CORE

V

CORE

V

CORE

MLPF MAV

SS

MAV

DD

V

SS

CLPF CAV

SS

CAV

DD

V

CORE

V

SS

RESET# SYREF

GNT0# REQ0# V

SS

V

IO

REQ2# IRQ13 GNT1# REQ1#

V

SS

V

IO

GNT2# SUPA#

INTA# AD31 V

SS

V

IO

AD27 CIS AD29 AD30

V

SS

V

IO

AD26 AD28

AD25 AD24 V

SS

V

IO

DRB20 DRB21 DRB22 V

SS

DRB11 V

SS

DRB0 DRB6 V

SS

DRB29 DRB24 V

SS

VID3 V

SS

V

CORE

V

SS

V

CORE

V

SS

AD1 V

SS

AD5 AD11 V

SS

AD14 IRDY# V

SS

CBE2# V

SS

AD23 AD22 CBE3#

DRB23 DRB8 V

IO

DRB12 DRB15 V

IO

DRB3 DRB7 V

IO

DRB28 DRB25 V

IO

VID4 V

IO

VID0 V

SS

PW1 V

IO

AD0 V

IO

AD6 CBE0# V

IO

AD15 STOP# V

IO

PA R A D16 V

IO

AD19 AD21

V

IO

V

SS

DRB9 DRB14 V

SS

DRB1 DRB4 V

SS

DRB31 DRB26 V

SS

VID7 VID5 V

SS

VID1 V

SS

TDN V

SS

AD4 AD3 V

SS

AD8 AD10 V

SS

DEVSL# TRDY# V

SS

AD17 AD20 V

SS

V

IO

V

SS

V

IO

DRB10 DRB13 V

IO

DRB2 DRB5 V

IO

DRB30 DRB27 V

IO

VIPCLK VID6 VIPSYNC VID2 V

SS

TDP PW0 AD7 AD2 V

IO

AD9 AD12 V

IO

AD13 CBE1# V

IO

FRAME#AD18 V

IO

V

SS

AMD Geode™

LX Processor

S

= GND Ball

= PWR Ball

= Strap Option Ball

= Multiplexed Ball

V

CORE

V

CORE

V

SS

V

SS

V

SS

V

CORE

V

CORE

V

CORE

V

CORE

V

SS

V

SS

V

SS

V

CORE

V

CORE

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

CORE

V

CORE

V

SS

V

SS

V

SS

V

CORE

V

CORE

V

CORE

V

CORE

V

SS

V

SS

V

SS

V

CORE

V

CORE

(Top View)

s

s

s

ss

s

s