364 AMD Geode™ LX Processors Data Book

Display Controller Register Descriptions

33234H

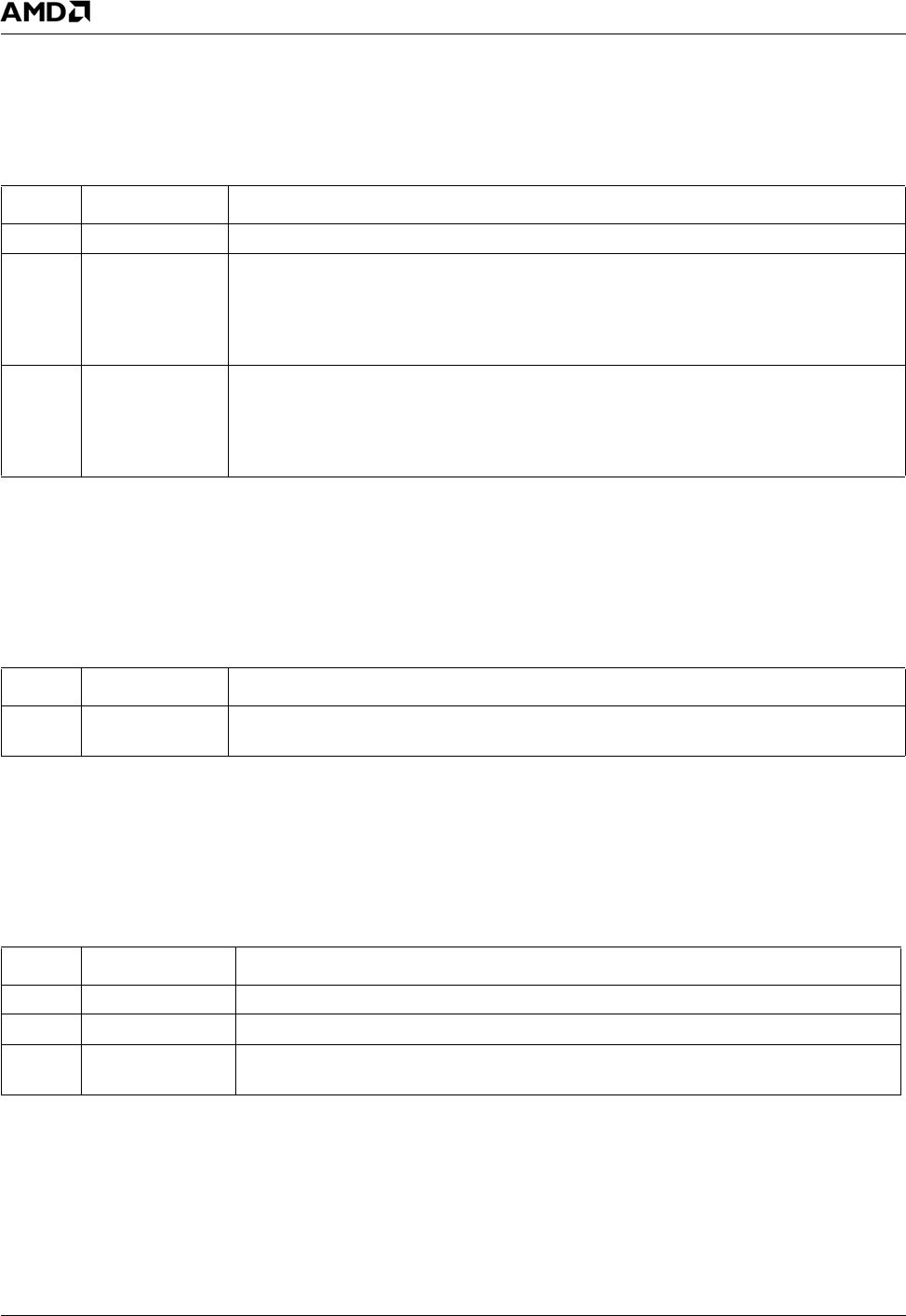

6.6.19.6 Horizontal Blank End

6.6.19.7 Horizontal Sync Start

6.6.19.8 Horizontal Sync End

Index 03h

Typ e R /W

Reset Value 00h

Horizontal Blank End Register Bit Descriptions

Bit Name Description

7 RSVD Reserved. Set to 1.

6:5 DISPEN_SKEW Display Enable Skew Control. This value is a binary encoded value that specifies how

many character clocks to skew the horizontal display enable signal by (0 character clocks

- 3 character clocks) before it is sent to the attribute controller. This field is used to

accommodate differences in the length of the video pipeline (frame buffer to pixel output)

in various text and graphics modes.

4:0 H_BLANK_END

[4:0]

Horizontal Blank End Register Bits [4:0]. This 6-bit value is a compare target for the

character count where the horizontal blank signal ends. Bit 5 of this value is in the Hori-

zontal Sync End register (Index 05h[7]). Note that not all horizontal counter bits are com-

pared, which can create aliased compares depending upon the binary values involved in

the count range and compare values.

Index 04h

Typ e R /W

Reset Value 00h

Horizontal Sync Start Register Bit Descriptions

Bit Name Description

7:0 H_SYNC_ST Horizontal Sync Start. This value specifies the character position where the horizontal

sync pulse starts.

Index 05h

Typ e R /W

Reset Value 00h

Horizontal Sync End Register Bit Descriptions

Bit Name Description

7 H_BLANK_END5 Horizontal Blank End bit 5. See H_BLANK_END[4:0] bit description (Index 03h[4:0]).

6:5 RSVD Not Implemented. (HSync Delay).

4:0 H_SYNC_END Horizontal Sync End. These bits represent the low five bits of the character position

where the horizontal sync signal ends.