AMD Geode™ LX Processors Data Book 89

5

CPU Core 33234H

5.0CPU Core

This section describes the internal operations of the

AMD Geode™ LX processor’s CPU Core from a program-

mer’s point of view. It includes a description of the tradi-

tional “core” processing and FPU operations. The

integrated function registers are described in the next

chapter.

The primary register sets within the processor core include:

• Application Register Set

• System Register Set

5.1 Core Processor Initialization

The CPU Core is initialized when the RESET# (Reset) sig-

nal is asserted. The CPU Core is placed in real mode and

the registers listed in Table 5-1 are set to their initialized

values. RESET# invalidates and disables the CPU cache,

and turns off paging. When RESET# is asserted, the CPU

terminates all local bus activity and all internal execution.

While RESET# is asserted, the internal pipeline is flushed

and no instruction execution or bus activity occurs.

Approximately 150 to 250 external clock cycles after

RESET# is de-asserted, the processor begins executing

instructions at the top of physical memory (address location

FFFFFFF0h). The actual number of clock cycles depends

on the clock scaling in use. Also, before execution begins,

an additional 2

20

clock cycles are needed when self-test is

requested.

Typically, an intersegment jump is placed at FFFFFFF0h.

This instruction forces the processor to begin execution in

the lowest 1 MB of address space. Table 5-1 lists the CPU

Core registers and illustrates how they are initialized.

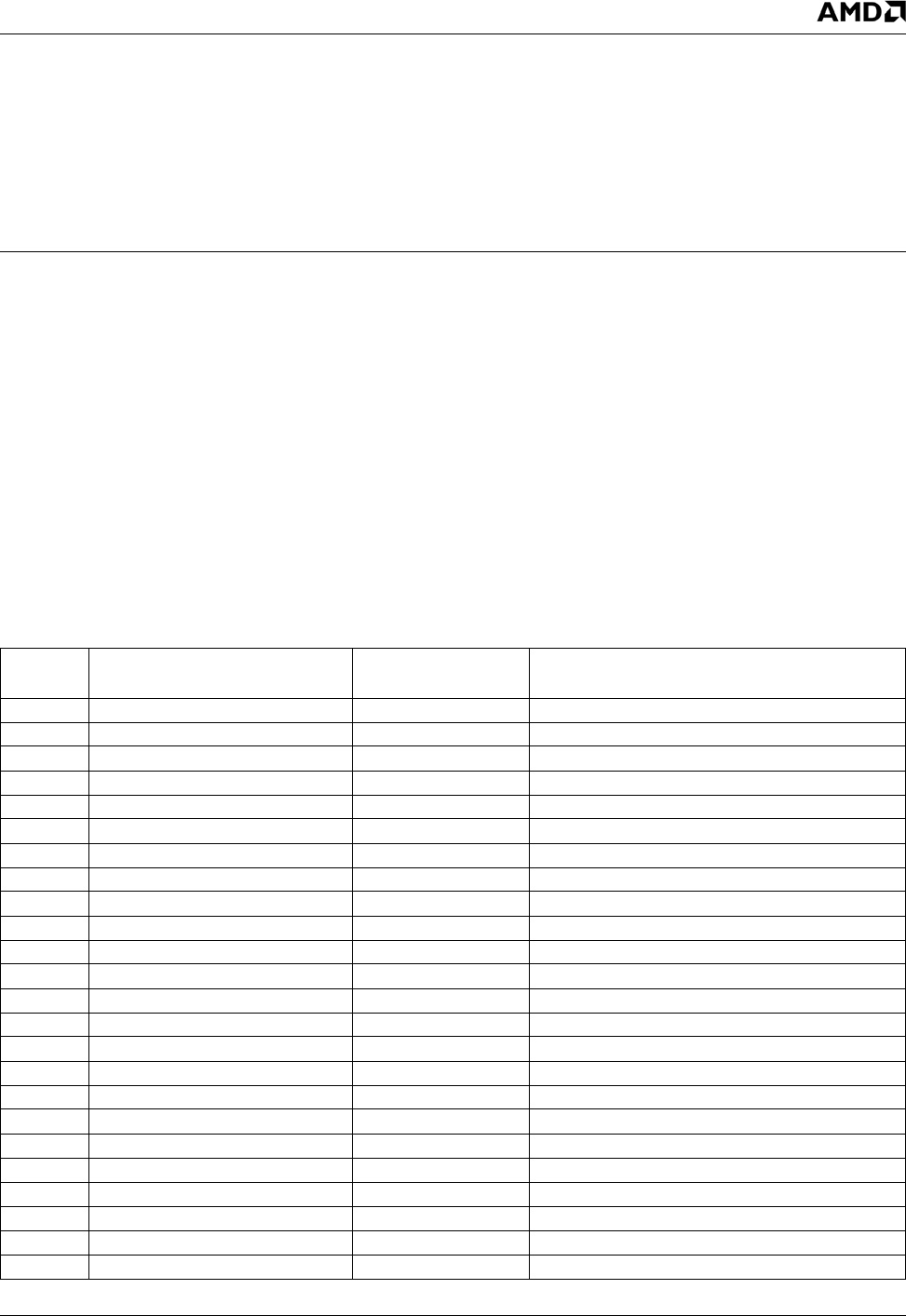

Table 5-1. Initialized Core Register Controls

Register Register Name

Initialized Contents

(Note 1) Comments

EAX Accumulator xxxxxxxxh 00000000h indicates self-test passed.

EBX Base xxxxxxxxh

ECX Count xxxxxxxxh

EDX Data xxxx 04 [DIR0]h DIR0 = Device ID

EBP Base Pointer xxxxxxxxh

ESI Source Index xxxxxxxxh

EDI Destination Index xxxxxxxxh

ESP Stack Pointer xxxxxxxxh

EFLAGS Extended Flags 00000002h See Table 5-4 on page 93 for bit definitions.

EIP Instruction Pointer 0000FFF0h

ES Extra Segment 0000h Base address set to 00000000h. Limit set to FFFFh.

CS Code Segment F000h Base address set to FFFF0000h. Limit set to FFFFh.

SS Stack Segment 0000h Base address set to 00000000h. Limit set to FFFFh.

DS Data Segment 0000h Base address set to 00000000h. Limit set to FFFFh.

FS Extra Segment 0000h Base address set to 00000000h. Limit set to FFFFh.

GS Extra Segment 0000h Base address set to 00000000h. Limit set to FFFFh.

IDTR Interrupt Descriptor Table Register Base = 0, Limit = 3FFh

GDTR Global Descriptor Table Register xxxxxxxxh

LDTR Local Descriptor Table Register xxxxh

TR Task Register xxxxh

CR0 Control Register 0 60000010h See Table 5-10 on page 96 for bit descriptions.

CR2 Control Register 2 xxxxxxxxh See Table 5-9 on page 96 for bit descriptions.

CR3 Control Register 3 xxxxxxxxh See Table 5-8 on page 96 for bit descriptions.

CR4 Control Register 4 00000000h See Table 5-7 on page 96 for bit descriptions.

Note 1. x = Undefined value.