AMD Geode™ LX Processors Data Book 49

GeodeLink™ Interface Unit

33234H

4.1.3.2 I/O Routing and Translation

I/O addresses are routed and are never translated. I/O

request routing is performed with a choice of two descriptor

types. Each GLIU may have any number of each descriptor

type. The IOD types satisfy different needs for various soft-

ware models.

Each I/O request is compared against all the IOD. If the I/O

request does not hit in any of the descriptors, the request is

sent to the subtractive port. If the I/O request hits more

than one descriptor, the results are undefined. Software

must provide a consistent non-overlapping I/O address

map. The methods of check and routing are described in

Table 4-4.

IOD Base Mask Descriptors (IOD_BM)

IOD_BM is the simplest descriptor. It usually maps a power

of two size aligned region of I/O to a destination ID.

IOD Swiss Cheese Descriptors (IOD_SC)

The IOD_SC maps an 8-byte region of memory in 1 byte

chunks to one of two devices. The descriptor type is useful

for legacy address mapping. The Swiss cheese feature

implies that the descriptor is used to “poke holes” in I/O.

4.1.3.3 Special Cycles

PCI special cycles are performed using I/O writes and set-

ting the BIZARRO flag in the write request. The BIZARRO

flag is treated as an additional address bit, providing

unaliased I/O address. The I/O descriptors are set up to

route the special cycles to the appropriate device (i.e.,

GLCP, GLPCI, etc.). The I/O descriptors are configured to

default to the appropriate device on reset. The PCI special

cycles are mapped as:

Name BIZZARO Address

Shutdown 1 00000000h

Halt 1 00000001h

x86 specific 1 00000002h

0003h-FFFFh 1 00000002h-0000FFFFh

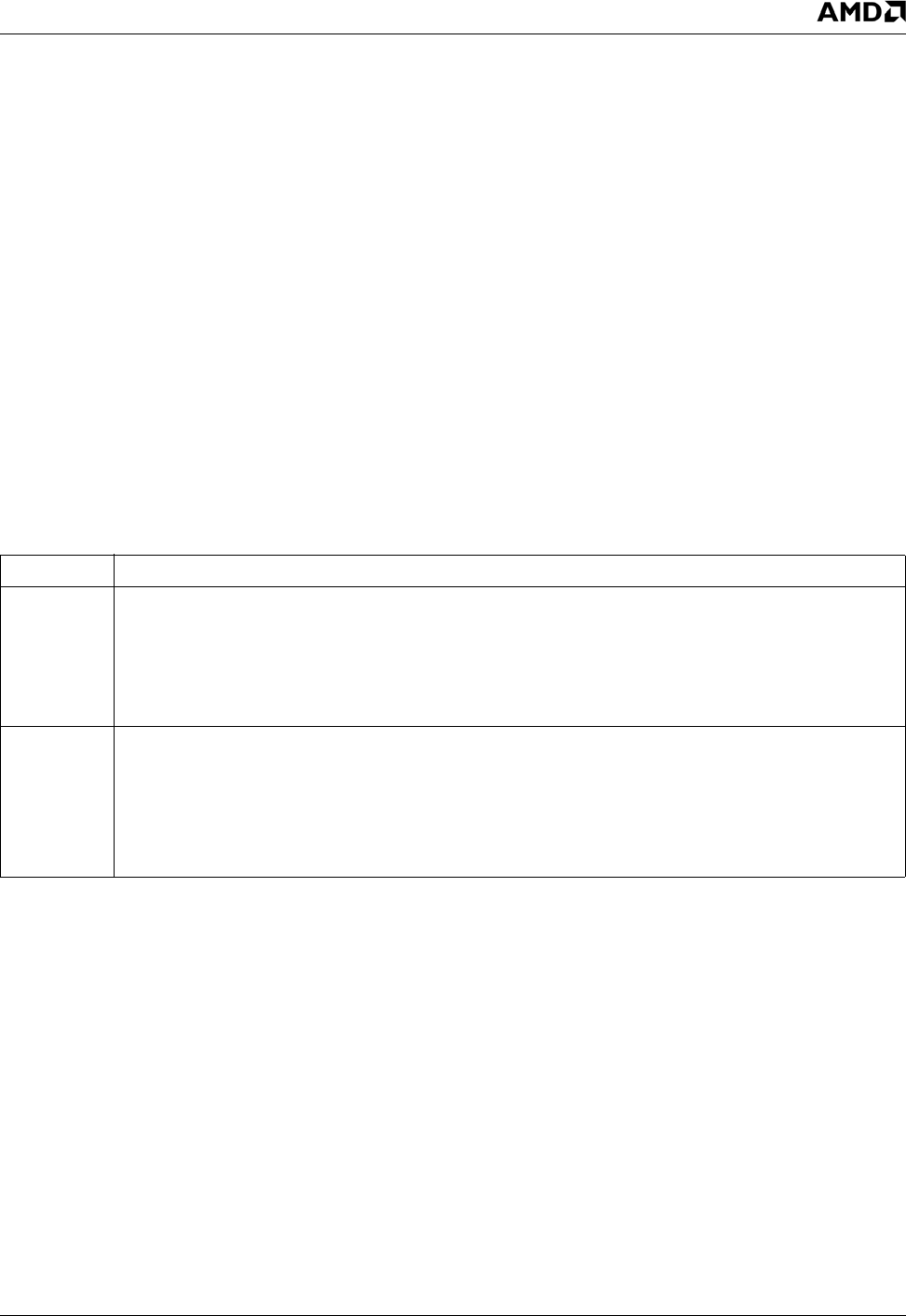

Table 4-4. GLIU I/O Descriptor Address Hit and Routing Description

Descriptor Function Description

IOD_BM Checks that the physical address supplied by the device on address bits [31:12] with a logic AND with PMASK bits of

the register bits [19:0] are equal to the PBASE bits of the descriptor register bits [39:20].

Also checks that the BIZZARO bit of the request is equal to the PCMP_PIZ bit of the descriptor register bit [60].

If the above matches, then the descriptor has a hit condition and routes the received address to the programmed des-

tination of the P2D_BM register bit [63:61].

DEVICE_ADDR = request address

IOD_SC Checks that the physical address supplied by the device’s request on address bits [31:18] are equal to the PBASE field

of descriptor register bits [13:0] and that the enable write or read conditions given by the descriptor register fields WEN

and REN in bits [47:32] and [31:16], respectively matches the request type and enable fields given on the physical

address bits [17:14] of the device’s request.

If the above matches, then the descriptor has a hit condition and routes the received address to the programmed des-

tination ID, PDID1 field of the descriptor register bits [63:61].

DEVICE_ADDR = request address