186 AMD Geode™ LX Processors Data Book

CPU Core Register Descriptions

33234H

5.5.2.93 Real Time Stamp Counter MSR (RTSC_MSR)

5.5.2.94 TSC and RTSC Low DWORDs MSR (RTSC_TSC_MSR)

MSR Address 00001910h

Typ e R /W

Reset Value 00000000_00000000h

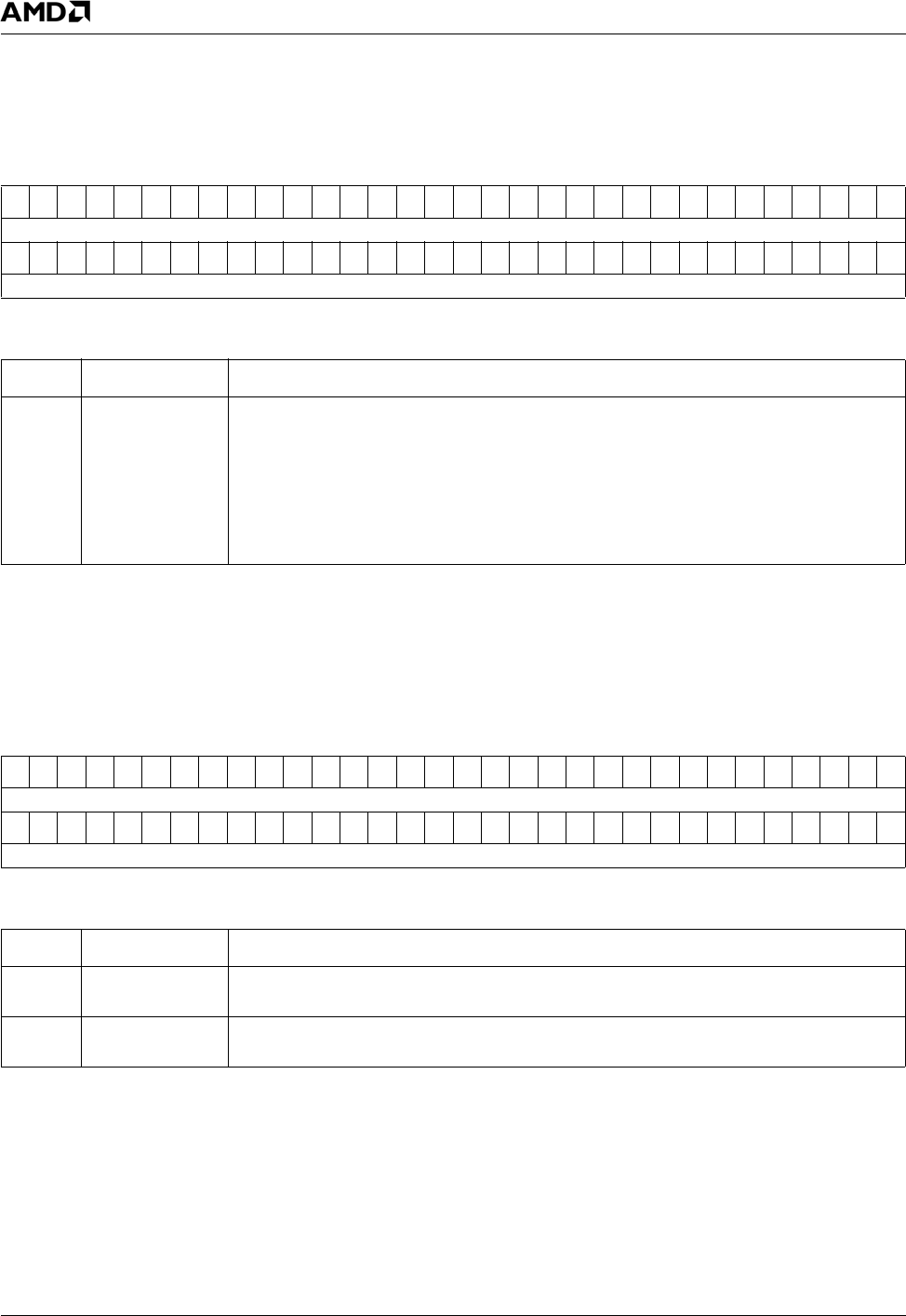

RTSC_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RTSC (High DWORD)

313029282726252423222120191817161514131211109876543210

RTSC (Low DWORD)

RTSC_MSR Bit Descriptions

Bit Name Description

63:0 RTSC Real Time Stamp Counter. This register is the 64-bit secondary, or “real” time stamp

counter. This counter allows software to configure the TSC not to include SMM or DMM

time, and still have an accurate real time measurement that includes these times.

BC_CONFIG0_MSR (MSR 00001900h) contains configuration bits that determine if the

RTSC counts during Suspend mode. It always counts during SMM and DMM modes.

All bits in this register are writable, unlike the TSC that clears the upper DWORD to 0 on

writes.

MSR Address 00001911h

Typ e RO

Reset Value 00000000_00000000h

RTSC_TSC_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RTSC_LOW

313029282726252423222120191817161514131211109876543210

TSC_LOW

RTSC_TSC_MSR Bit Descriptions

Bit Name Description

63:32 RTSC_LOW Real Time Stamp Counter Low DWORD. This field provides a synchronized snapshot

of the low DWORD of the RTSC register (MSR 00001910h).

31:0 TSC_LOW Time Stamp Counter Low DWORD. This field provides a synchronized snapshot of the

low DWORD of the TSC register (MSR 00000010h).