AMD Geode™ LX Processors Data Book 579

GeodeLink™ PCI Bridge Register Descriptions

33234H

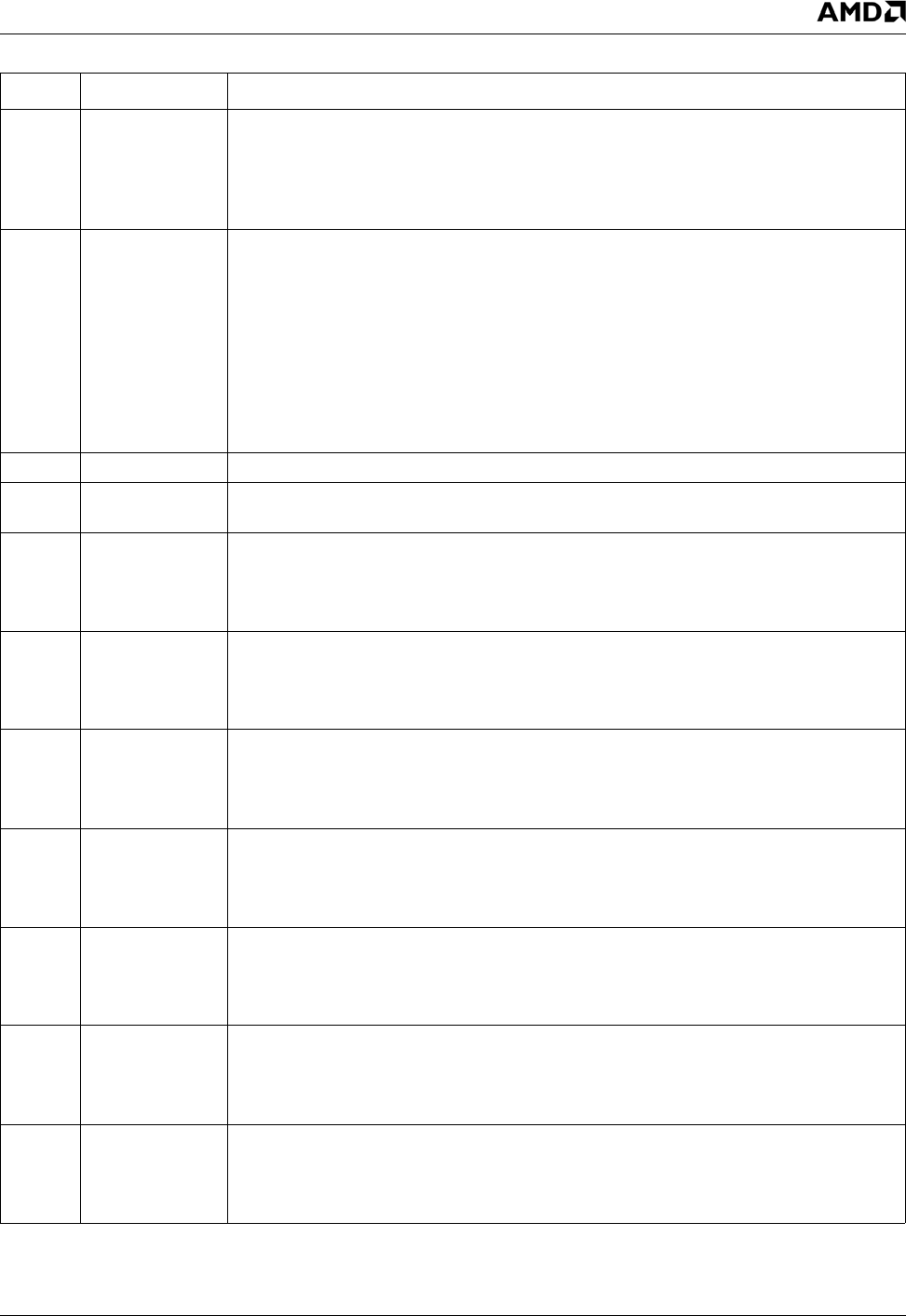

42 SLTO Subsequent Latency Timeout Select. Specifies the subsequent target latency timeout

limit. If within a burst, the GLPCI module does not respond with the configured number of

clock ticks, the PCI interface will terminate the PCI bus cycle.

0: 8 PCI clock edges

1: 4 PCI clock edges

41:40 ILTO Initial Latency Timeout Select. Specifies the initial target latency timeout limit for the

PCI interface. If the GLPCI module does not respond with the first data phase within the

configured number of clock edges, the PCI interface will terminate the PCI bus cycle.

If AILTO (MSR 5000201Fh[6]) = 0

00: 32 PCI clock edges 10: 8 PCI clock edges

01: 16 PCI clock edges 11: 4 PCI clock edges

If AILTO = 1

00: 64 PCI clock edges 10: 256 PCI clock edges

01: 128 PCI clock edges 11: No timeout

39:35 LAT PCI Latency Timer. Latency timeout value for limiting bus tenure.

34:32 0 (RO) Constant 0 (Read Only). The three least significant bits of the PCI latency timer field are

fixed as zeros. These bits are not used as part of the PCI latency timer comparison.

31 PE PCI Error. Allow detection of either a parity error or a system error to be reported in the

PARE bit (MSR 50002003h[21]).

0: Disable.

1: Enable.

30 BME Broken Master Error. Allow detection of a broken PCI bus master to be reported in the

BME bit (MSR 50002003h[18]).

0: Disable.

1: Enable.

29 TARE Target Abort Received Error. Allow reception of a PCI bus target abort to be reported in

the TARE bit (MSR 50002003h[17]).

0: Disable.

1: Enable.

28 MARE Master Abort Received Error. Allow reception of a PCI bus master abort to be reported

in the MARE bit (MSR 50002003h[16]).

0: Disable.

1: Enable.

27 PS PCI ASMI. Allow detection of either a parity error or a system error to be reported in the

PARE bit (MSR 50002002h[21]).

0: Disable.

1: Enable.

26 BMS Broken Master ASMI. Allow detection of a broken PCI bus master to be reported in the

BME bit (MSR 50002002h[18]).

0: Disable.

1: Enable.

25 TARS Target Abort Received ASMI. Allow reception of a PCI bus target abort to be reported in

the TARE bit (MSR 50002002h[17]).

0: Disable.

1: Enable.

GLPCI_CTRL Bit Descriptions (Continued)

Bit Name Description