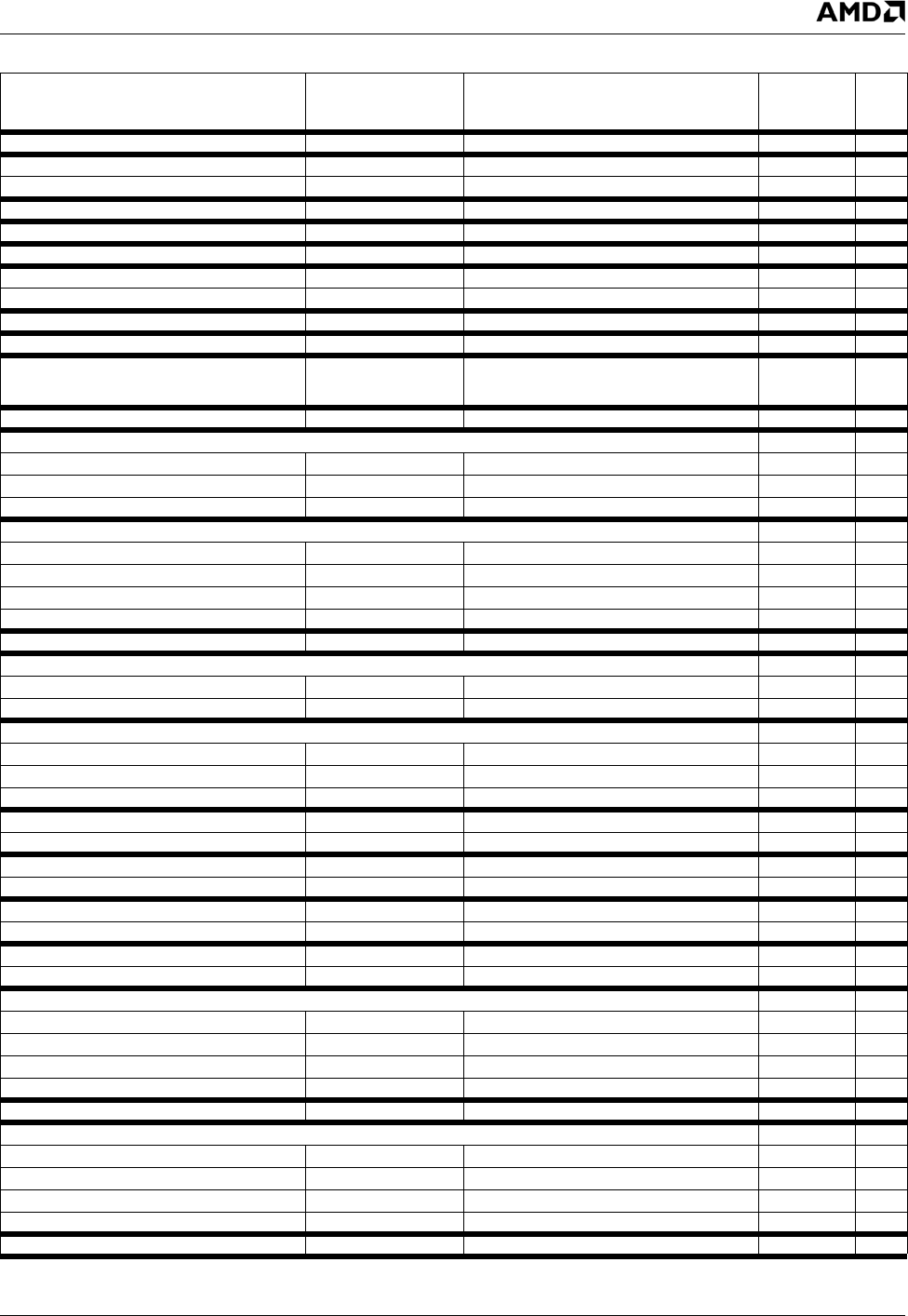

AMD Geode™ LX Processors Data Book 669

Instruction Set

33234H

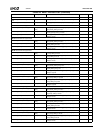

FPATAN Function Eval: Tan-1(y/x) D9 F3 ST(1) <--- ATAN[ST(1) / TOS]; then pop TOS 269 - 354 3

FPREM Floating Point Remainder D9 F8 TOS <--- Rem[TOS / ST(1)] 53 - 208

FPREM1 Floating Point Remainder IEEE D9 F5 TOS <--- Rem[TOS / ST(1)] 53 - 208

FPTAN Function Eval: Tan(x) D9 F2 TOS <--- TAN(TOS); then push 1.0 onto stack 217 - 232 1, 2

FRNDINT Round to Integer D9 FC TOS <--- Round(TOS) 12

FRSTOR Load FPU Environment and Register DD [mod 100 r/m] Restore state 19 2

FSAVE Save FPU Environment and Register (9B)DD [mod 110 r/m] Wait, then save state 19 2

FNSAVE Save FPU Environment and Register DD [mod 110 r/m] Save state 19 2

FSCALE Floating Multiply by 2n D9 FD TOS <--- TOS

× 2

(ST(1))

3

FSIN Function Evaluation: Sin(x) D9 FE TOS <--- SIN(TOS) 130 - 215 1

FSINCOS Function Eval.: Sin(x)& Cos(x) D9 FB temp <--- TOS;

TOS <--- SIN(temp); then

push COS(temp) onto stack

345 - 374 1, 2

FSQRT Floating Point Square Root D9 FA TOS <--- Square Root of TOS 13/54

FST Store FPU Register

FPU Stack DD [1101 0 n] ST(n) <--- TOS 1 3

64-bit Real DD [mod 010 r/m] M.DR <--- TOS 6

32-bit Real D9 [mod 010 r/m] M.SR <--- TOS 1/4

FSTP Store FPU Register, Pop

FPU Stack DB [1101 1 n] ST(n) <--- TOS; then pop TOS 1 3

80-bit Real DB [mod 111 r/m] M.XR <--- TOS; then pop TOS 1 3

64-bit Real DD [mod 011 r/m] M.DR <--- TOS; then pop TOS 6

32-bit Real D9 [mod 011 r/m] M.SR <--- TOS; then pop TOS 1/4

FBSTP Store BCD Data, Pop DF [mod 110 r/m] M.BCD <--- TOS; then pop TOS 82

FIST Store Integer FPU Register

32-bit Integer DB [mod 010 r/m] M.SI <--- TOS 4

16-bit Integer DF [mod 010 r/m] M.WI <--- TOS 3

FISTP Store Integer FPU Register, Pop

64-bit Integer DF [mod 111 r/m] M.LI <--- TOS; then pop TOS 6

32-bit Integer DB [mod 011 r/m] M.SI <--- TOS; then pop TOS 4

16-bit Integer DF [mod 011 r/m] M.WI <--- TOS; then pop TOS 3

FSTCW Store FPU Mode Control Register (9B)D9 [mod 111 r/m] Wait Memory <--- Control Mode Register 1 2

FNSTCW Store FPU Mode Control Register D9 [mod 111 r/m] Memory <--- Control Mode Register 1 2

FSTENV Store FPU Environment (9B)D9 [mod 110 r/m] Wait Memory <--- Env. Registers 1 2

FNSTENV Store FPU Environment D9 [mod 110 r/m] Memory <--- Env. Registers 1 2

FSTSW Store FPU Status Register (9B)DD [mod 111 r/m] Wait Memory <--- Status Register 1 2

FNSTSW Store FPU Status Register DD [mod 111 r/m] Memory <--- Status Register 1 2

FSTSW AX Store FPU Status Register to AX (9B)DF E0 Wait AX <--- Status Register 1 2

FNSTSW AX Store FPU Status Register to AX DF E0 AX <--- Status Register 1 2

FSUB Floating Point Subtract

Top of Stack DC [1110 1 n] ST(n) <--- ST(n) - TOS 1/6

80-bit Register D8 [1110 0 n] TOS <--- TOS - ST(n 1/6

64-bit Real DC [mod 100 r/m] TOS <--- TOS - M.DR 1/6

32-bit Real D8 [mod 100 r/m] TOS <--- TOS - M.SR 1/6

FSUBP Floating Point Subtract, Pop DE [1110 1 n] ST(n) <--- ST(n) - TOS; then pop TOS 1/6

FSUBR Floating Point Subtract Reverse

Top of Stack DC [1110 0 n] TOS <--- ST(n) - TOS 1/6

80-bit Register D8 [1110 1 n] ST(n) <--- TOS - ST(n) 1/6

64-bit Real DC [mod 101 r/m] TOS <--- M.DR - TOS 1/6

32-bit Real D8 [mod 101 r/m] TOS <--- M.SR - TOS 1/6

FSUBRP Floating Point Subtract Reverse, Pop DE [1110 0 n] ST(n) <--- TOS - ST(n); then pop TOS 1/6

Table 8-29. FPU Instruction Set (Continued)

FPU Instruction Opcode Operation

Clock Ct

Single/Dbl

(or extended) Notes