538 AMD Geode™ LX Processors Data Book

GeodeLink™ Control Processor

33234H

GIO_PCI Serial Protocol

The GIO can override the functionality of its SUSP# pin to

create a serial bus called CPU Interface Serial (CIS). The

reset mode for this pin is the SUSP# function. To properly

operate as the CIS interface, the CISM bit in MSR

51000010h[4:3] in the companion device must be pro-

grammed for Mode C. Notice that all the input signals are

active low. They are all inverted inside the GIO and con-

verted to active high signals. The protocol is shown in Table

6-84. The SUSP# pin must always be parked as inactive or

1.

Serial packets are expected whenever the companion

device signals transitions. Back to back serial packets can

occur once the entire serial packet has completed. The

AMD Geode LX processor decoded signals are guaran-

teed to transition only after the entire completion of the

packet, although they may transition during the transmis-

sion of the packet.

SUSP#/CIS Pin Initialization

The SUSP# function must NOT be active until the initializa-

tion code can set the CISM bits in the companion device to

set the correct companion device mode.

GIO_SMI Synchronization

If the companion device generates a synchronous SMI in

response to a specific CPU initiated instruction (I/O), the

SMI# signal is transmitted to the processor before the com-

pletion of the PCI cycle. Therefore, the companion device

must not complete read or write cycles until it has transmit-

ted the SMI. The design guarantees that if the PCI cycle

completes on the PCICLK after the SMI transmission, the

SMI will reach the processor before the I/O completion

response. Therefore, the processor can handle the SMI

before completing the instruction.

GIO_A20M

GIO_A20M is emulated with an SMI. The processor

receives an SMI from the companion device on I/Os that

modify the state of A20M. The SMI handler must then write

to MSR_A20M (MSR 4C000031h) in the GIO to trigger a

real A20M signal back to the processor. When the instruc-

tion completes, A20M is asserted.

GIO_NMI

The GIO_NMI signal is the real NMI from the companion

device.

GIO_INPUT_DIS, GIO_OUTPUT_DIS

GIO_INPUT_DIS and GIO_OUTPUT_DIS are part of the

GLIU power management. See the AMD Geode™ CS5536

Companion Device Data Book (publication ID 33238) for

details.

GIO_INIT

GIO_INIT is triggered via MSR 4C000033h in the GLCP for

all companion device modes. INIT is used to reset the

CPU. It is NOT a CPU soft reset.

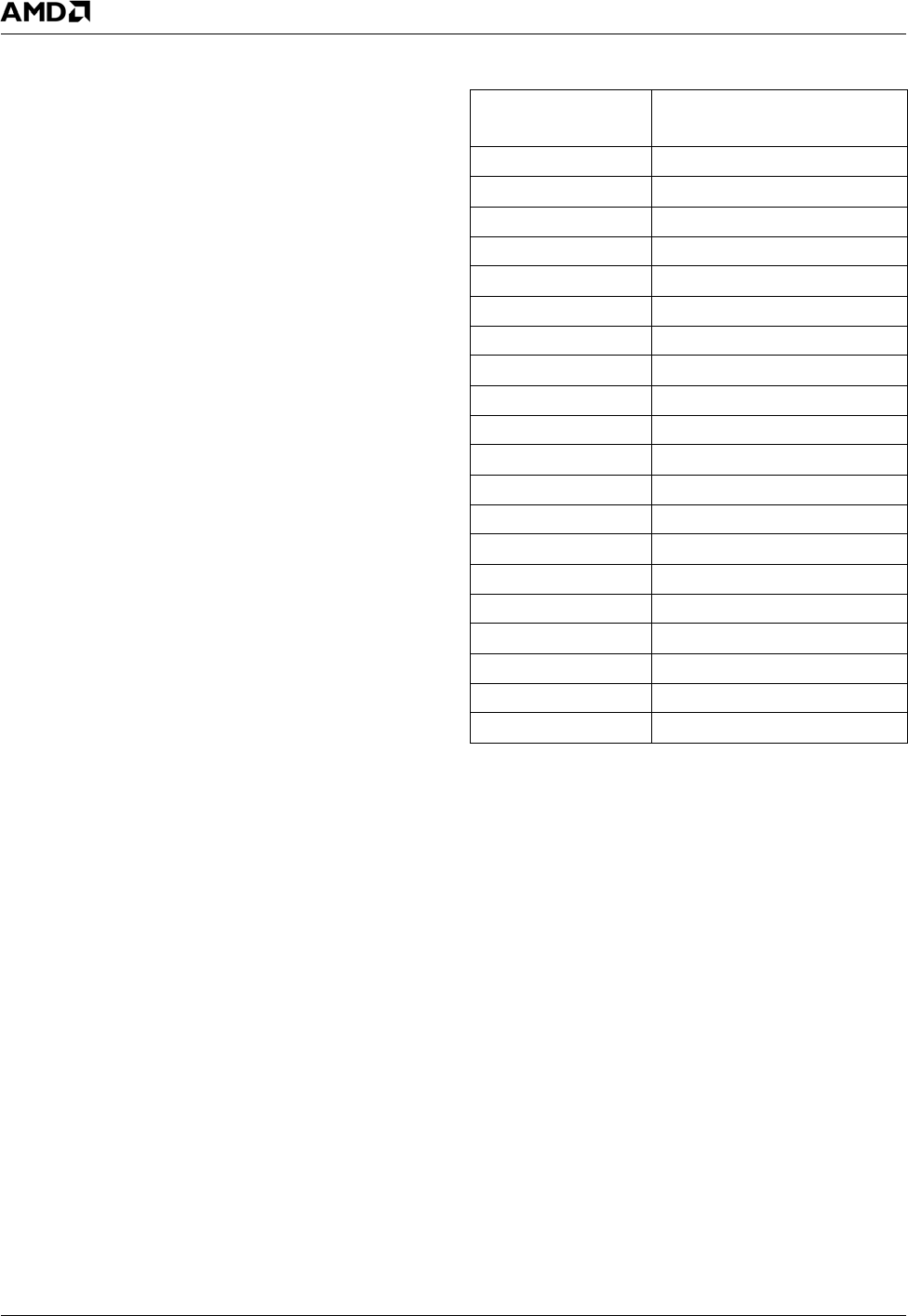

Table 6-84. CIS Signaling Protocol

Phase

Bit Definition

(GIO CIS Mode C)

0 (START) 0

1 (START) 0

2 RSVD

3 RSVD

4 SUSP#

5NMI#

6 INPUT_DIS#

7 OUTPUT_DIS#

8SMI#

9 INTR#

10 1

11 1

12 1

13 1

14 1

15 1

16 1

17 1

18 (END) 1

19 (END) 1