644 AMD Geode™ LX Processors Data Book

Instruction Set

33234H

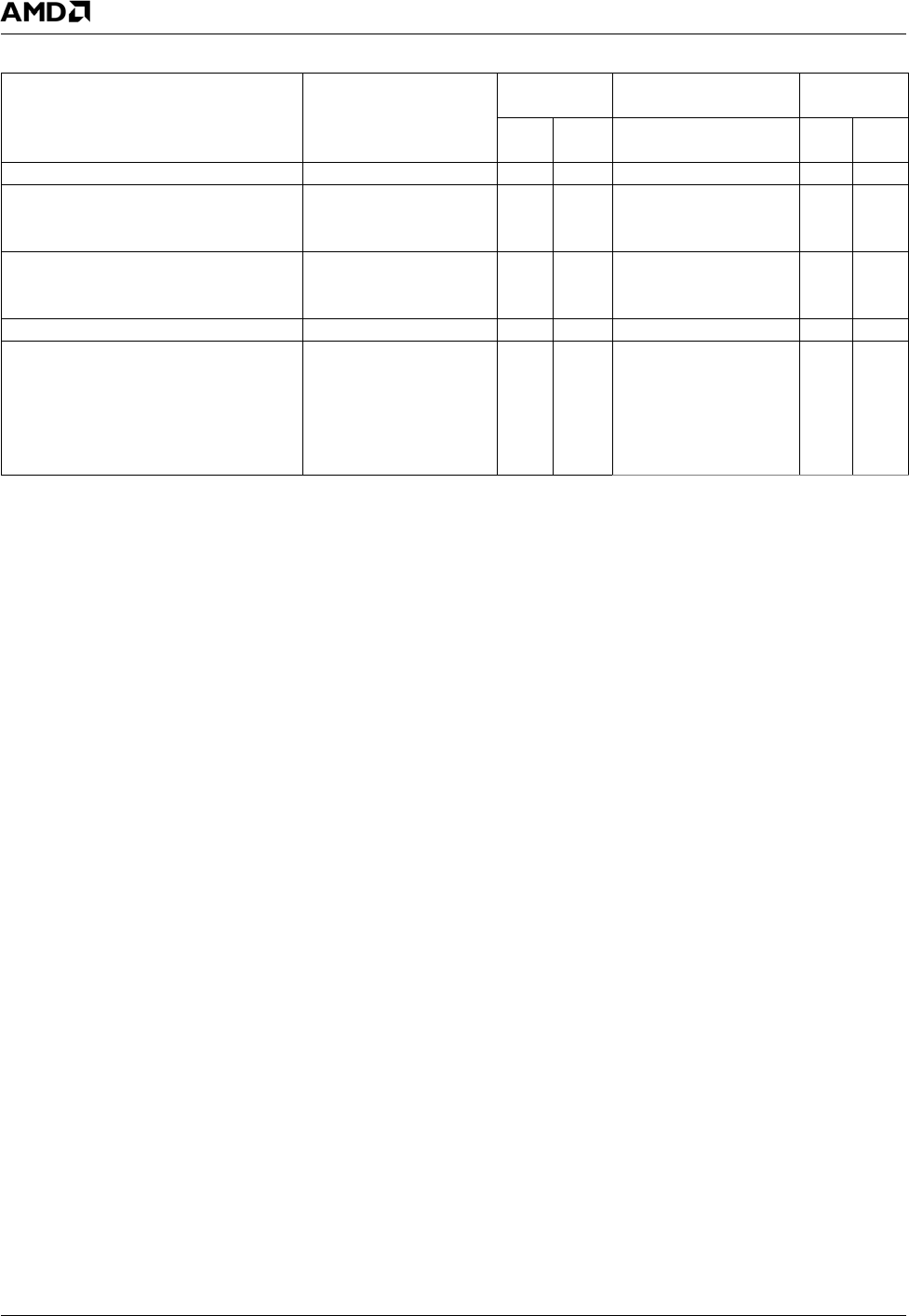

WRMSR Write to Model Specific Register 0F 30 10 10 ---------

XADD Exchange and Add x- --xxxxx

Register1, Register2 0F C[000w] [11 reg2 reg1] 2 2

Memory, Register 0F C[000w] [mod reg r/m] 2 2

XCHG Exchange --------- b,f f,h

Register/Memory with Register 8[011w] [mod reg r/m] 2 2

Register with Accumulator 9[0 reg] 2 2

XLAT Translate Byte D7 4 4 --------- h

XOR Boolean Exclusive OR 0--- xxux0 b h

Register to Register 3 [00dw] [11 reg r/m] 1 1

Register to Memory 3 [000w] [mod reg r/m] 1 1

Memory to Register 3 [001w] [mod reg r/m] 1 1

Immediate to Register/Memory 8 [00sw] [mod 110 r/m] ### 1 1

Immediate to Accumulator (short form) 3 [010w] ### 1 1

Note 1. The instructions, RDTSC, RDPMC, and RDMSR all have the effect of serializing with pending memory requests. For example, a

RDTSC will not complete until any pending line fills or prefetches have completed. This is an artifact of the AMD Geode CPU and

GeodeLink architecture since out-of-order read responses are not supported.

Table 8-26. Processor Core Instruction Set (Continued)

Instruction Opcode

Clock Count

(Reg/Cache Hit) Flags

Notes

Real

Mode

Prot’d

Mode

ODI TSZ APC

FFFFFFFFF

Real

Mode

Prot’d

Mode