270 AMD Geode™ LX Processors Data Book

Graphics Processor Register Definitions

33234H

6.4.2.16 Base Offset (GP_BASE_OFFSET)

This register is used to define the physical base addresses of the regions used for all GP read and write operations to mem-

ory. Each base defines a 16 MB region that begins on a 4 MB boundary. Thus the top two bits of the offset [23:22] are

added to the base to identify the correct 4 MB region in memory for a given transfer. Because there are different bases

defined for each potential source of data, each can come from a different memory region. If a memory operation goes

beyond the 16 MB region that has been assigned, it wraps back to the beginning of the 16 MB region.

6.4.2.17 Command Top (GP_CMD_TOP)

This register defines the starting address of the command buffer within the command buffer region. Bits [23:0] of this regis-

ter are combined with the CBASE in GLD_MSR_CONFIG (MSR A0002001h) to form the 32-bit address. This register

should only be changed when the GP is not actively executing out of the command buffer, which can be checked by reading

the CE bit in the GP_BLT_STATUS register (GP Memory Offset 44h[4]) or by verifying that GP_CMD_READ (GP Memory

Offset 58h) and GP_CMD_WRITE (GP Memory Offset 5Ch) have the same value.

GP_HST_SRC Bit Descriptions

Bit Name Description

31:0 HST_SRC Host Source Data. Used during BLT in host source mode.

GP Memory Offset 4Ch

Typ e R /W

Reset Value 01004010h

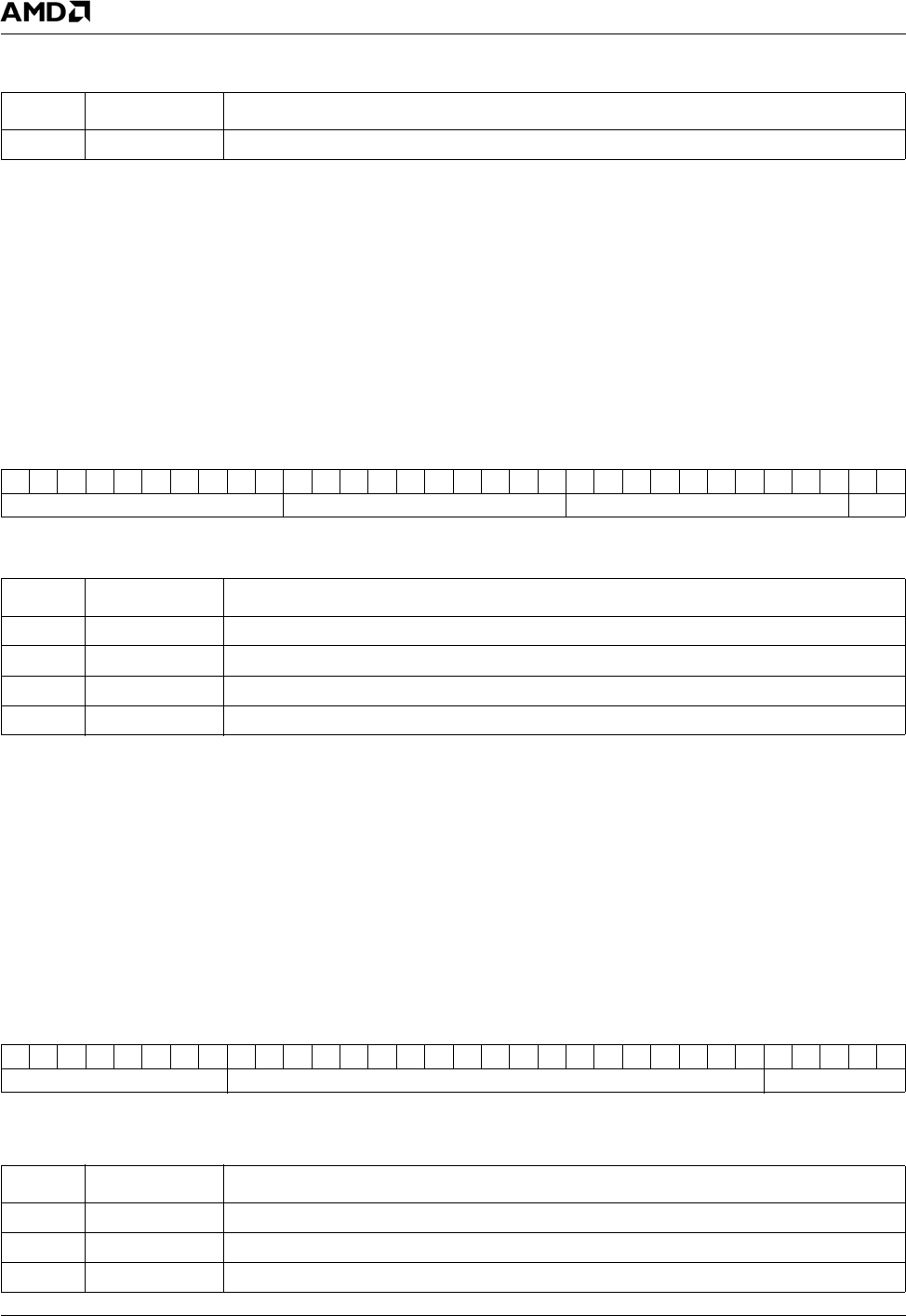

GP_BASE_OFFSET Register Map

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DBASE SBASE CH3BASE RSVD

GP_BASE_OFFSET Bit Descriptions

Bit Name Description

31:22 DBASE Destination Base. Base address of destination data region in physical memory.

21:12 SBASE Source Base. Base address of source data region in physical memory.

11:2 CH3BASE Channel 3 Base. Base address of channel 3 data region in physical memory.

1:0 RSVD Reserved.

GP Memory Offset 50h

Typ e R /W

Reset Value 01000000h

GP_CMD_TOP Register Map

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD CMD_TOP RSVD

GP_CMD_TOP Bit Descriptions

Bit Name Description

31:24 RSVD Reserved. Read returns 0.

23:5 CMD_TOP Command Top. Starting address of the command buffer in the command buffer region.

4:0 RSVD Reserved. Read returns 0.