494 AMD Geode™ LX Processors Data Book

Video Input Port Register Descriptions

33234H

6.10.2.4 VIP Interrupt (VIP_INT)

VIP Memory Offset 0Ch

Typ e R /W

Reset Value xxxxFFFEh

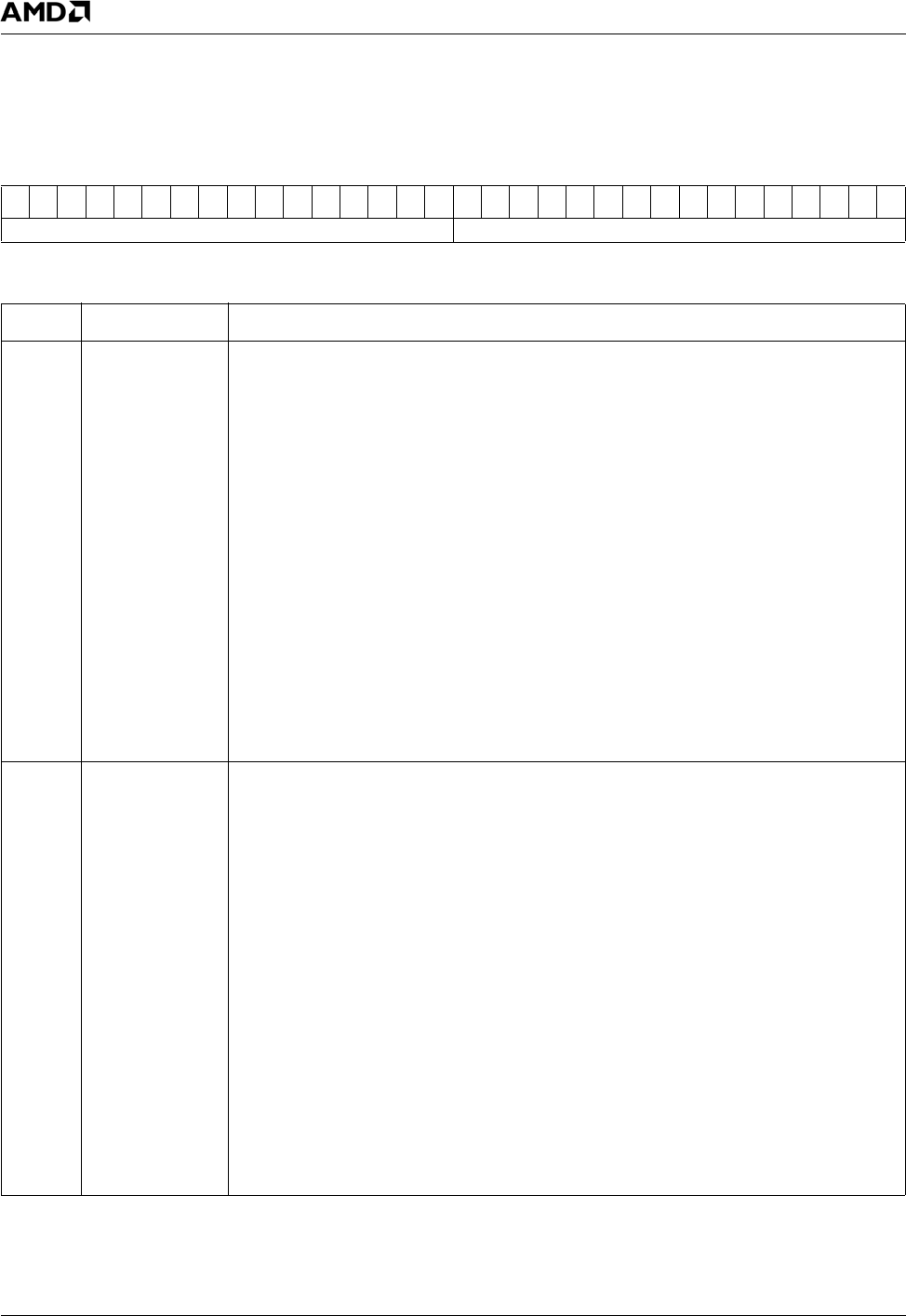

VIP_INT Register Map

313029282726252423222120191817161514131211109876543210

INT_STATUS INT_MASK

VIP_INT Bit Descriptions

Bit Name Description

31:16 INT_STATUS VIP Interrupt Status.

0: INT not pending.

1: INT pending.

Writing a 1 to this bit clears the status.

Bit 30: FIFO line wrap error.

Bit 29: FIFO overflow error.

Bit 28: FIFO threshold hit.

Bit 27: Long line (> 3000 clocks) error.

Bit 26: Vertical timing error (frame error or address error)/Msg missed error.

Bit 25: Active pixels per line error.

Bit 24: VIP clock input error.

Bit 23: Ancillary checksum or parity error.

Bit 22: Msg buffer full or ancillary threshold packet count reached.

Bit 21: End of vertical blanking.

Bit 20: Start of vertical blanking.

Bit 19: Start of even field.

Bit 18: Start of odd field.

Bit 17: Current line = VIP Line Target (see Current/Target Line register).

Bit 16: Not used (0).

15:0 INT_MASK VIP Interrupt Masks.

0: Enable, unmask the INT.

1: Disabled, mask the INT.

Bit 14: When enabled (0), allows FIFO line wrap error INT.

Bit 13: When enabled (0), allows FIFO overflow error INT.

Bit 12: When enabled (0), allows FIFO threshold hit INT.

Bit 11: When enabled (0), allows Long line (> 3000 clocks) error INT.

Bit 10: When enabled (0), allows vertical timing error (frame error or address error) INT.

Bit 9: When enabled (0), allows the active pixel input video error INT.

Bit 8: When enabled (0),allows the VIP clock input error INT.

Bit 7: When enabled (0), allows ancillary checksum or parity error INT.

Bit 6: When enabled (0), allows msg buffer full INT or ancillary threshold packet count

reached INT.

Bit 5: When enabled (0), allows end of vertical blanking INT.

Bit 4: When enabled (0), allows start of vertical blanking INT.

Bit 3: When enabled (0), allows start of even field INT.

Bit 2: When enabled (0), allows start of odd field INT.

Bit 1: When enabled (0), allows current line = VIP Line Target INT (see Current/Target

Line register).

Bit 0: Not used (R/W).