578 AMD Geode™ LX Processors Data Book

GeodeLink™ PCI Bridge Register Descriptions

33234H

6.16.2 GLPCI Specific Registers

6.16.2.1 GLPCI Global Control (GLPCI_CTRL)

MSR Address 50002010h

Typ e R /W

Reset Value 44000000_00000000h

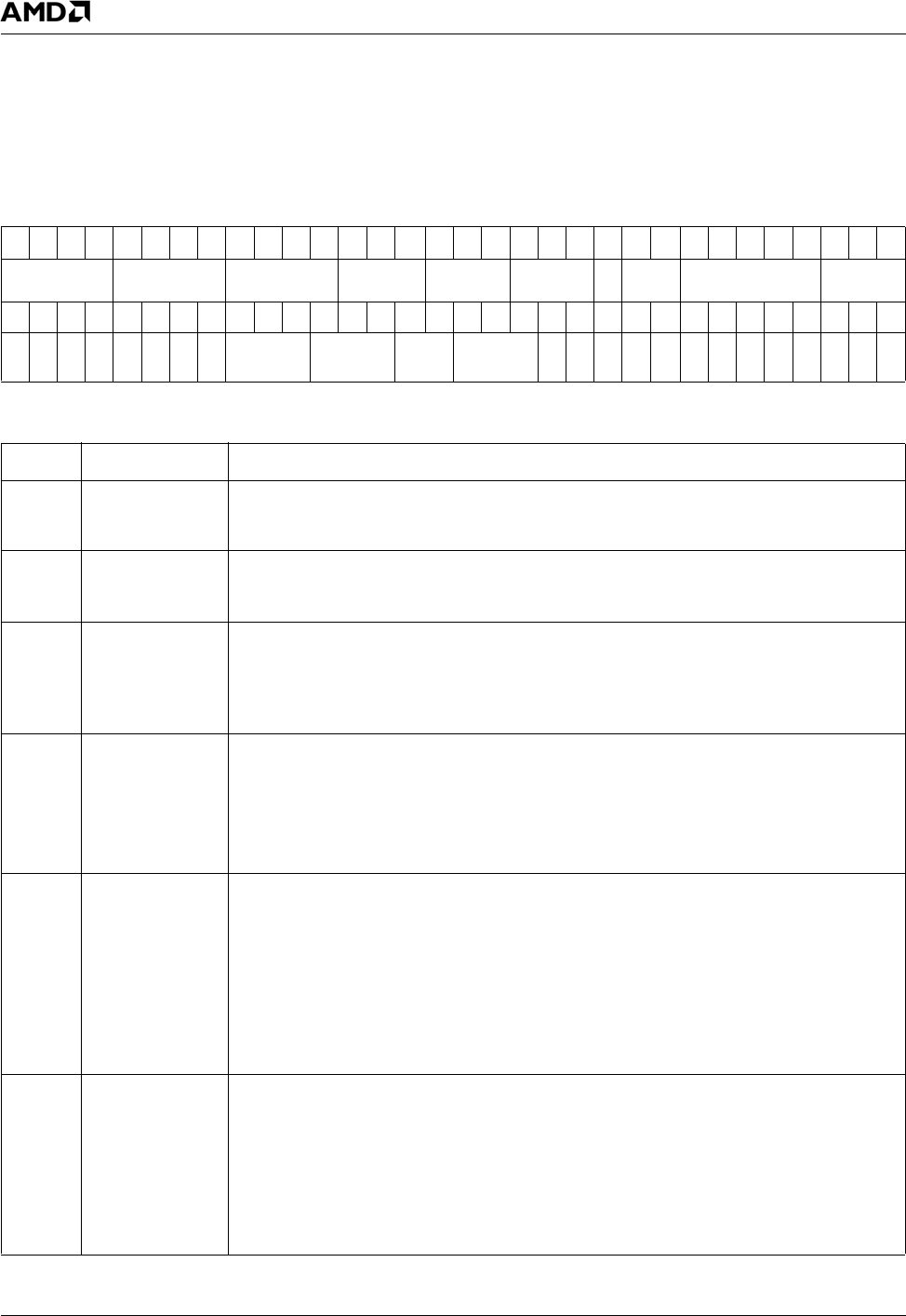

GLPCI_CTRL Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

FTH RTH SBRTH RTL DTL WTO

SLTO

ILTO LAT 0

313029282726252423222120191817161514131211109876543210

PE

BME

TARE

MARE

PS

BMS

TARS

MARS

SUS IRFT IRFC IOD

ST

ER

RHE

LDE

RUPO

BZ

NI

ISO

OWC

IWC

PCD

IE

ME

GLPCI_CTRL Bit Descriptions

Bit Name Description

63:60 FTH In-Bound Flush Threshold. Controls the timing for requesting new read data while con-

currently flushing previously prefetched, stale read data. If the number of prefetched 64-

bit WORDs reaches this level then a pending request will be made.

59:56 RTH In-Bound Read Threshold. Controls the timing for prefetching read data. If the number

of prefetched 32-bit WORDs reaches this threshold, a subsequent GLIU request will be

generated to fetch the next cache line of read data.

55:52 SBRTH Southbridge In-Bound Read Threshold. Controls the timing for prefetching read data

for the AMD Geode™ companion device. If the number of prefetched 32-bit WORDs

reaches this threshold, a subsequent GLIU request will be generated to fetch the next

cache line of read data. The status of the companion device’s GNT# pin (GNT2#) is sam-

pled to determine when the companion device is generating an in-bound request.

51:49 RTL Retry Transaction Limit. Limits the number of out-bound retries. If a target signals retry

indefinitely, the PCI interface may be configured to abort the failing out-bound request.

000: No limit 100: 64 retries

001: 8 retries 101: 128 retries

010: 16 retries 110: 256 retries

011: 32 retries 111: 512 retries

48:46 DTL Delayed Transaction Limit. Limits the duration of delayed transactions. Once a read

transaction is delayed (retried before the first data phase has completed) all other in-

bound transactions are rejected until the original request is satisfied. If the original master

stops retrying, a live-lock condition may occur. If the number of rejected transactions

reaches the limit defined by this field, then the delayed transaction is forgotten.

000: No limit 100: 16 rejections

001: 2 rejections 101: 32 rejections

010: 4 rejections 110: 64 rejections

011: 8 rejections 111: 128 rejections

45:43 WTO In-Bound Write Timeout. Controls the flushing of in-bound posted write data. When an

in-bound write has completed on the PCI bus, an internal counter is loaded with a value

derived from this field. It will then count down on each PCI clock edge. When the counter

reaches 0, the posted write data is flushed to memory.

000: 4 PCI clock edge 100: 64 PCI clock edges

001: 8 PCI clock edge 101: 128 PCI clock edges

010: 16 PCI clock edge 110: 256 PCI clock edges

011: 32 PCI clock edges 111: No timeout