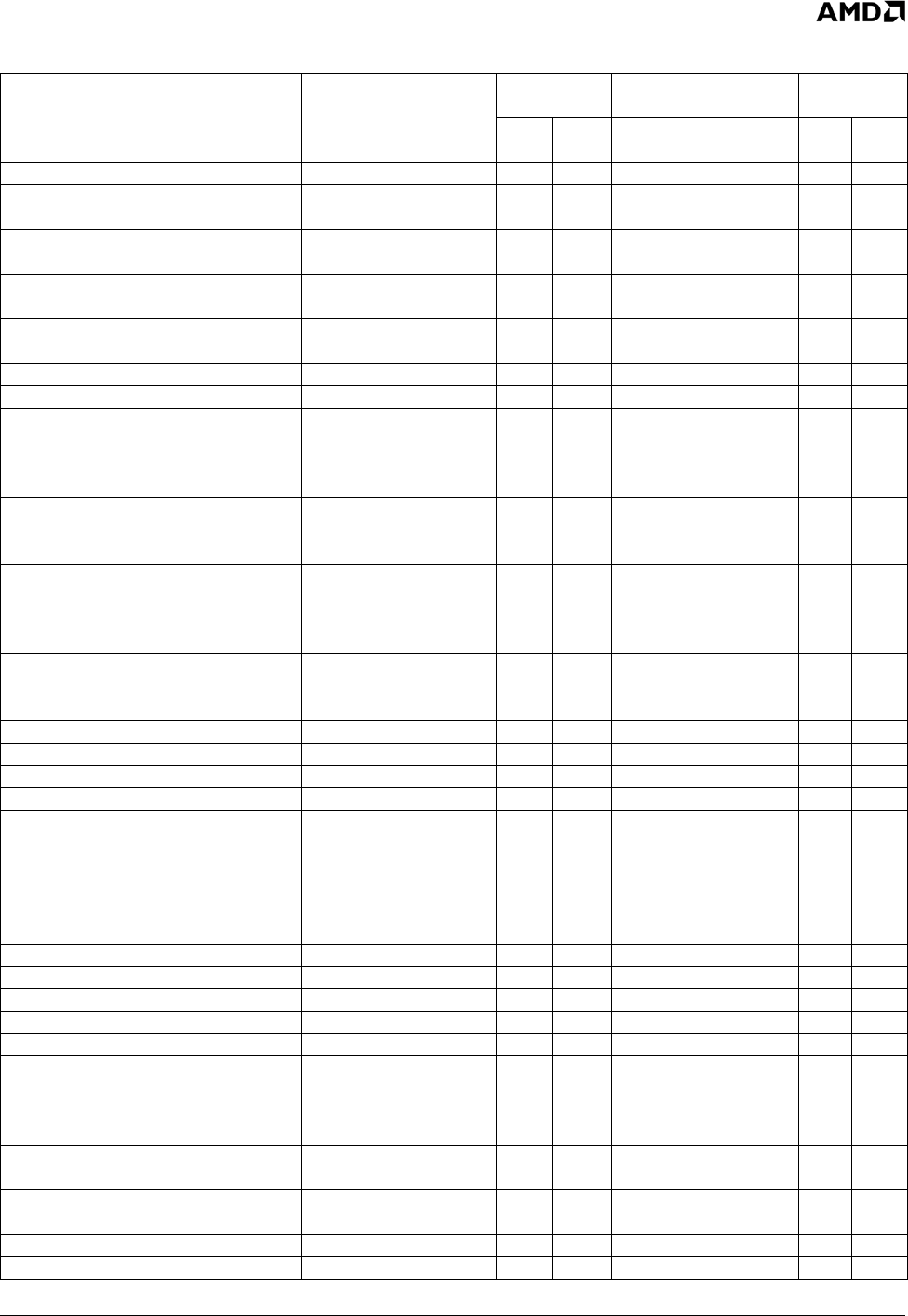

AMD Geode™ LX Processors Data Book 643

Instruction Set

33234H

SFENCE 11

SGDT Store GDT Register b,c h

To Register/Memory 0F 01 [mod 000 r/m] 6 6 ---------

SIDT Store IDT Register b,c h

To Register/Memory 0F 01 [mod 001 r/m] 6 6 ---------

SLDT Store LDT Register ah

To Register/Memory 0F 00 [mod 000 r/m] 1 ---------

STR Store Task Register ah

To Register/Memory 0F 00 [mod 001 r/m] 3 ---------

SMSW Store Machine Status Word 0F 01 [mod 100 r/m] 2 2 --------- b,c h

STOS Store String A [101w] 2 2 --------- b h

SHL Shift Left Logical bh

Register/Memory by 1 D [000w] [mod 100 r/m] 1 1 x ---xxuxx

Register/Memory by CL D [001w] [mod 100 r/m] 2 2 u ---xxuxx

Register/Memory by Immediate C [000w] [mod 100 r/m] # 1 1 u ---xxuxx

SHLD Shift Left Double u---xxuxx b h

Register/Memory by Immediate 0F A4 [mod reg r/m] # 2 1

Register/Memory by CL 0F A5 [mod reg r/m] 2 1

SHR Shift Right Logical bh

Register/Memory by 1 D [000w] [mod 101 r/m] 2 1 x ---xxuxx

Register/Memory by CL D [001w] [mod 101 r/m] 2 1 u ---xxuxx

Register/Memory by Immediate C [000w] [mod 101 r/m] # 2 1 u ---xxuxx

SHRD Shift Right Double u---xxuxx b h

Register/Memory by Immediate 0F AC [mod reg r/m] # 2 1

Register/Memory by CL 0F AD [mod reg r/m] 2 1

SMINT Software SMM Entry 0F 38 56-58 56-58 000000000 s,u s,u

STC Set Carry Flag F9 1 1 --------1

STD Set Direction Flag FD 2 2 -1-------

STI Set Interrupt Flag FB 1 1 --1------ m

SUB Integer Subtract x --- xxxxx b h

Register to Register 2 [10dw] [11 reg r/m] 1 1

Register to Memory 2 [100w] [mod reg r/m] 1 1

Memory to Register 2 [101w] [mod reg r/m] 1 1

Immediate to Register/Memory 8 [00sw] [mod 101 r/m] ### 1 1

Immediate to Accumulator (short form) 2 [110w] ### 1 1

SVDC Save Segment Register and Descriptor 0F 78 [mod sreg3 r/m] 7 7 --------- s,u s,u

SVLDT Save LDTR and Descriptor 0F 7A [mod 000 r/m] 7 7 --------- s,u s,u

SVTS Save TSR and Descriptor 0F 7C [mod 000 r/m] 8 8 --------- s,u s,u

SYSENTER Fast System Call Entry 0F 34 10 10 ---------

SYSEXIT

Fast System Call Exit 0F 35 11 11 ---------

TEST Test Bits 0 ---xxux0 b h

Register/Memory and Register 8 [010w] [mod reg r/m] 1 1

Immediate Data and Register/Memory F [011w] [mod 000 r/m] ### 1 1

Immediate Data and Accumulator A [100w] ### 1 1

VERR Verify Read Access -----x--- a g,h,j,p

To Register/Memory 0F 00 [mod 100 r/m] 8

VERW Verify Write Access -----x--- a g,h,j,p

To Register/Memory 0F 00 [mod 101 r/m] 8

WAIT Wait Until FPU Not Busy 9B 1 1 ---------

WBINVD Writeback and Invalidate Cache 0F 09 16+ 16+ --------- t t

Table 8-26. Processor Core Instruction Set (Continued)

Instruction Opcode

Clock Count

(Reg/Cache Hit) Flags

Notes

Real

Mode

Prot’d

Mode

ODI TSZ APC

FFFFFFFFF

Real

Mode

Prot’d

Mode