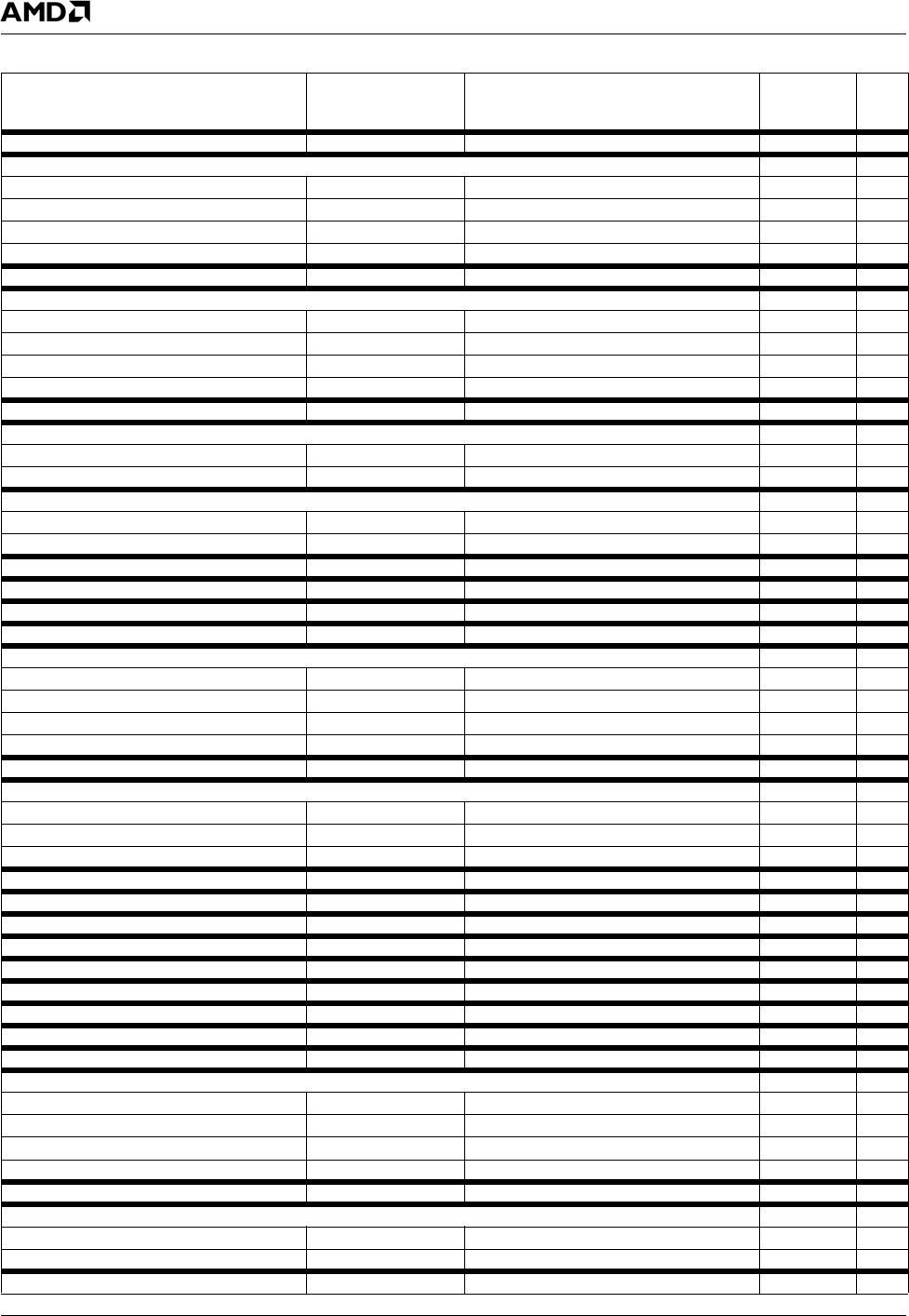

668 AMD Geode™ LX Processors Data Book

Instruction Set

33234H

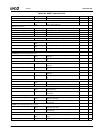

FDECSTP Decrement Stack pointer D9 F6 Decrement top of stack pointer 1 3

FDIV Floating Point Divide

Top of Stack DC [1111 1 n] ST(n) <--- ST(n) / TOS 12/47

80-bit Register D8 [1111 0 n] TOS <--- TOS / ST(n) 12/47

64-bit Real DC [mod 110 r/m] TOS <--- TOS / M.DR 12/47

32-bit Real D8 [mod 110 r/m] TOS <--- TOS / M.SR 12/47

FDIVP Floating Point Divide, Pop DE [1111 1 n] ST(n) <--- ST(n) / TOS; then pop TOS 12/47

FDIVR Floating Point Divide Reversed

Top of Stack DC [1111 0 n] TOS <--- ST(n) / TOS 12/47

80-bit Register D8 [1111 1 n] ST(n) <--- TOS / ST(n) 12/47

64-bit Real DC [mod 111 r/m] TOS <--- M.DR / TOS 12/47

32-bit Real D8 [mod 111 r/m] TOS <--- M.SR / TOS 12/47

FDIVRP Floating Point Divide Reversed, Pop DE [1111 0 n] ST(n) <--- TOS / ST(n); then pop TOS 12/47

FIDIV Floating Point Integer Divide

32-bit Integer DA [mod 110 r/m] TOS <--- TOS / M.SI 13/48

16-bit Integer DE [mod 110 r/m] TOS <--- TOS / M.WI 13/48

FIDIVR Floating Point Integer Divide Reversed

32-bit Integer DA [mod 111 r/m] TOS <--- M.SI / TOS 13/48

16-bit Integer DE [mod 111 r/m] TOS <--- M.WI / TOS 13/48

FFREE Free Floating Point Register DD [1100 0 n] TAG(n) <--- Empty 1 3

FINCSTP Increment Stack Pointer D9 F7 Increment top-of-stack pointer 1 3

FINIT Initialize FPU (9B)DB E3 Wait, then initialize 1 2

FNINIT Initialize FPU DB E3 Initialize 1 2

FLD Load Data to FPU Register

Top of Stack D9 [1100 0 n] Push ST(n) onto stack 1 3

80-bit Real DB [mod 101 /m] Push M.XR onto stack 1 3

64-bit Real DD [mod 000 r/m] Push M.DR onto stack 1 3

32-bit Real D9 [mod 000 r/m] Push M.SR onto stack 1 3

FBLD Load Packed BCD Data to FPU Register DF [mod 100 r/m] Push M.BCD onto stack 28

FILD Load Integer Data to FPU Register

64-bit Integer DF [mod 101 r/m] Push M.LI onto stack 4

32-bit Integer DB [mod 000 r/m] Push M.SI onto stack 1

16-bit Integer DF [mod 000 r/m] Push M.WI onto stack 1

FLD1 Load Floating Const.= 1.0 D9 E8 Push 1.0 onto stack 1 3

FLDCW Load FPU Mode Control Register D9 [mod 101 r/m] Ctl Word <--- Memory 1 3

FLDENV Load FPU Environment D9 [mod 100 r/m] Env Regs <--- Memory 1 3

FLDL2E Load Floating Const.= Log2(e) D9 EA Push Log

2

(e) onto stack 1 3

FLDL2T Load Floating Const.= Log2(10) D9 E9 Push Log

2

(10) onto stack 1 3

FLDLG2 Load Floating Const.= Log10(2) D9 EC Push Log

10

(2) onto stack 1 3

FLDLN2 Load Floating Const.= Ln(2) D9 ED Push Log

e

(2) onto stack 1 3

FLDPI Load Floating Const.= π D9 EB Push

π onto stack 1 3

FLDZ Load Floating Const.= 0.0 D9 EE Push 0.0 onto stack 1 3

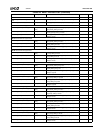

FMUL Floating Point Multiply

Top of Stack DC [1100 1 n] ST(n) <--- ST(n) × TOS 1/10

80-bit Register D8 [1100 1 n] TOS <--- TOS × ST(n) 1/10

64-bit Real DC [mod 001 r/m] TOS <--- TOS × M.DR 1/10

32-bit Real D8 [mod 001 r/m] TOS <--- TOS × M.SR 1/10

FMULP Floating Point Multiply & Pop DE [1100 1 n] ST(n) <--- ST(n)

× TOS; then pop TOS 1/10

FIMUL Floating Point Integer Multiply

32-bit Integer DA [mod 001 r/m] TOS <--- TOS

× M.SI 2/11

16-bit Integer DE [mod 001 r/m] TOS <--- TOS

× M.WI 2/11

FNOP No Operation D9 D0 No Operation 1 3

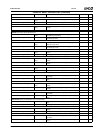

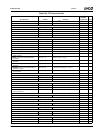

Table 8-29. FPU Instruction Set (Continued)

FPU Instruction Opcode Operation

Clock Ct

Single/Dbl

(or extended) Notes