AMD Geode™ LX Processors Data Book 171

CPU Core Register Descriptions

33234H

If paging is enabled, the region properties can be further modified by the PCD and PWT flags in the page table entry. The

PCD flag is OR’d with the CD bit of the region properties, and the PWT bit is OR’d with the WT bit of the region properties.

A similar combination is performed during tablewalks using the PCD/PWT bits from CR3 for the DTE access and the

PCD/PWT bits from the DTE for the PTE access. The net effect is that the WC and WS flags may actually be used even for

a region that is marked cacheable if a page table mapping later forces it to be uncacheable. For regions that are write-com-

bined, the PWT flag in the page table can be used to force write-burstable properties for selected pages.

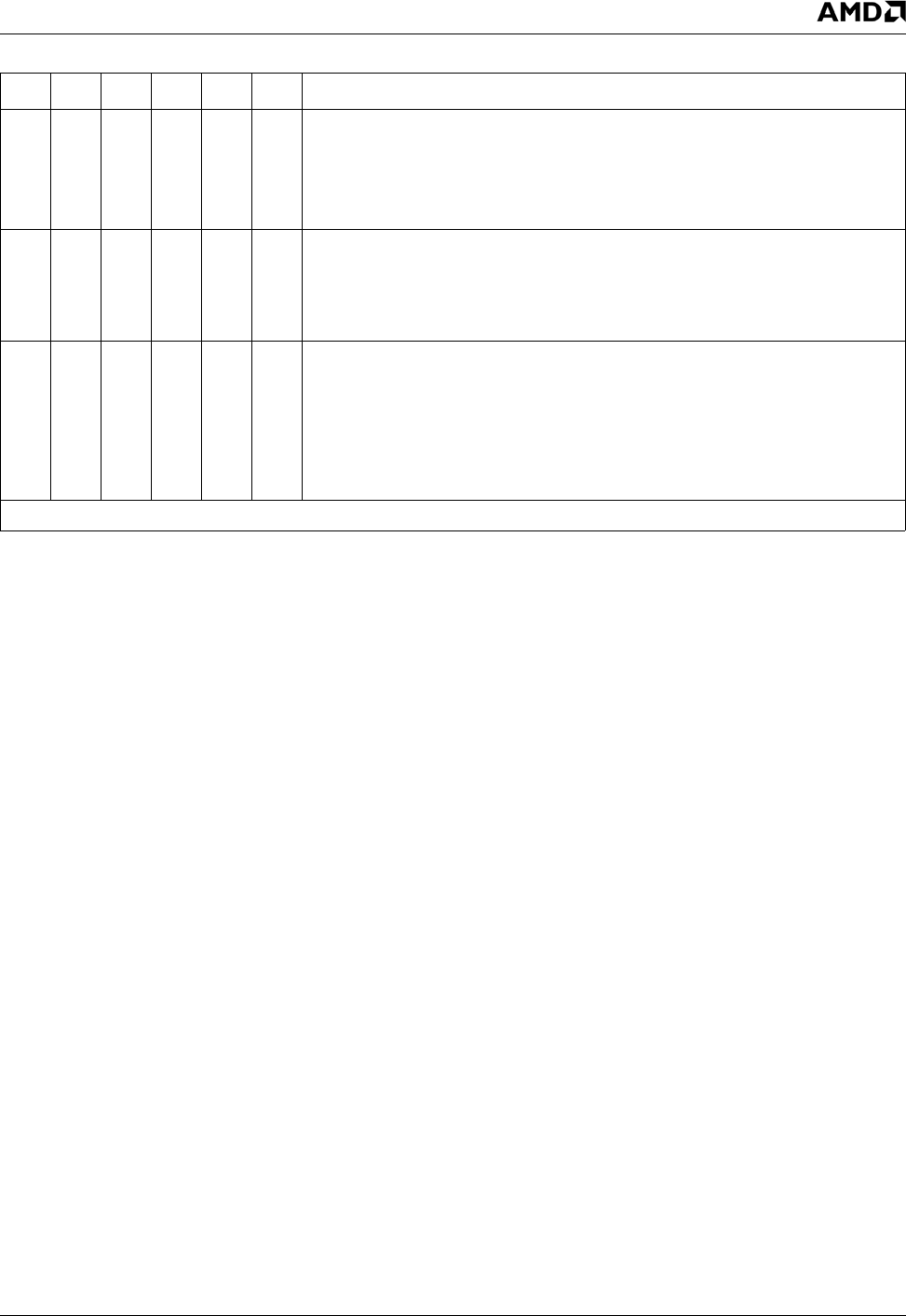

110001Write-combined (uncacheable). Writes to the same cache line may be com-

bined. Multiple writes to the same byte results in a single write with the last

value specified. Write order is not preserved; ideal for use with frame buffers.

Write-serialize. Limit the number of outstanding writes to the value of the

WSREQ field in DM_CONFIG0_MSR (MSR 00001800h[46:44]).

011001Write-burstable (uncacheable). Writes to the same cache line are combined

as long as they are to increasing addresses and do not access a previously

written byte. Multiple writes to the same byte results in multiple bytes on the

bus. The semantics match write bursting on PCI and should therefore be suit-

able for accessing memory-mapped devices.

111001Write-burstable (uncacheable). Writes to the same cache line are combined

as long as they are to increasing addresses and do not access a previously

written byte. Multiple writes to the same byte results in multiple bytes on the

bus. The semantics match write bursting on PCI and should therefore be suit-

able for accessing memory-mapped devices.

Write-serialize. Limit the number of outstanding writes to the value of the

WSREQ field in DM_CONFIG0_MSR (MSR 00001800h[46:44]).

Note: “x” indicates setting or clearing this bit has no effect.

Table 5-17. Write Operations vs. Region Properties (Continued)

WS WC WT WP WA CD Description