AMD Geode™ LX Processors Data Book 269

Graphics Processor Register Definitions

33234H

6.4.2.14 Status and Reset (GP_BLT_STATUS, GP_RESET)

This register is used to provide software with the current status of the GP in regards to operations pending and currently

executing. A write to this register has no effect unless byte 3 is 69h, which causes a reset of the GP, losing all state informa-

tion and discarding any active or pending BLT or vector. This is only intended to be used during debug to restore the GP in

the event of a hang. It is not required as part of the initialization or power on sequence for GP.

6.4.2.15 Host Source (GP_HST_SRC)

This register is used by software to load source data that is not originated in the frame buffer memory region. When per-

forming a BLT that requires host source data, software should first set up all of the configuration registers that are required

and initiate the BLT by writing to the GP_BLT_MODE register (GP Memory Offset 40h). This initiates the BLT in hardware,

which then waits for writes to the GP_HST_SRC register. Software should then perform enough writes to this register to

complete the BLT operation. Writes to this register are moved immediately into the source FIFO, allowing the CPU to per-

form successive writes. The EH bit in the GP_BLT_STATUS (GP Memory Offset 44h[5]) register indicates that the GP can

accept another cache line (32 bytes) of data.

This register is also aliased to the address range 100h-3FFh to allow the processor to move large blocks of data to the GP

through the repeat MOVS instruction. The GP throttles the incoming data by holding off register writes on the GLIU when

the source FIFO is full.

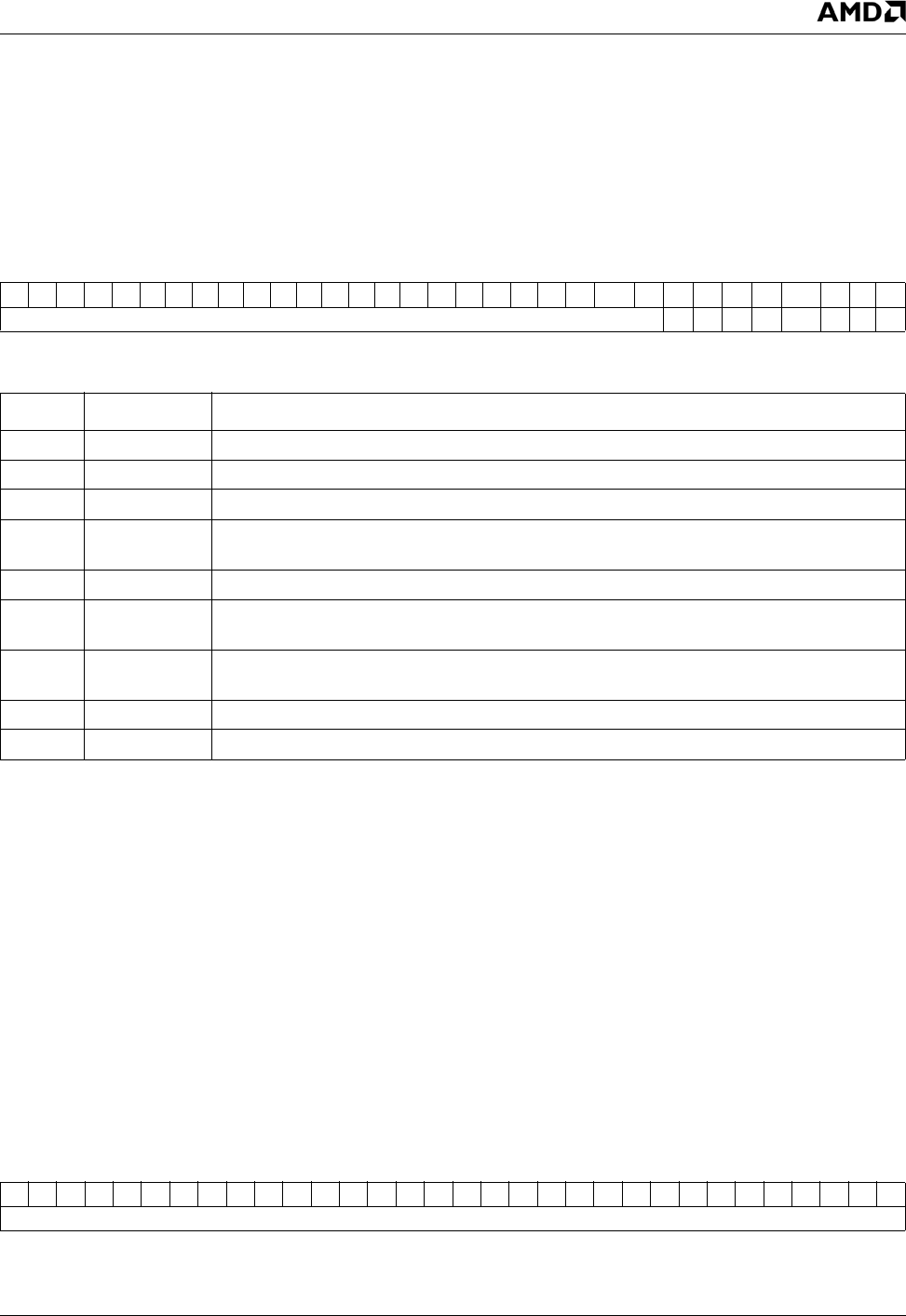

GP Memory Offset 44h

Typ e RO

Reset Value 00000008h

GP_BLT_STATUS Register Map

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD UF RP EH CE SHE PP IN PB

GP_BLT_STATUS Bit Descriptions

Bit Name Description

31:8 RSVD Reserved.

7UF Underflow. If bit is set, Channel 3 had too few pixels to complete the BLT.

6RP Read Pending. If bit is set, read request is waiting for data from GLIU.

5EH Expecting Host Source Data. If bit is set, current BLT is expecting to receive host source

data on Channel 3.

4CE Command Buffer Empty. If bit is set, read and write pointers are equal.

3SHE Source FIFO Half Empty. If bit is set, source FIFO can accept another cache line of host

source data.

2PP Primitive Pending. If bit is set, a second BLT or vector is in the queue behind the currently

executing operation.

1IN Interrupt Pending. If bit is set, the GP interrupt signal is active.

0PB Primative Busy. If bit is set, an operation is currently executing in the GP.

GP Memory Offset 48h

Typ e WO

Reset Value xxxxxxxxh

GP_HST_SRC Register Map

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

HST_SRC