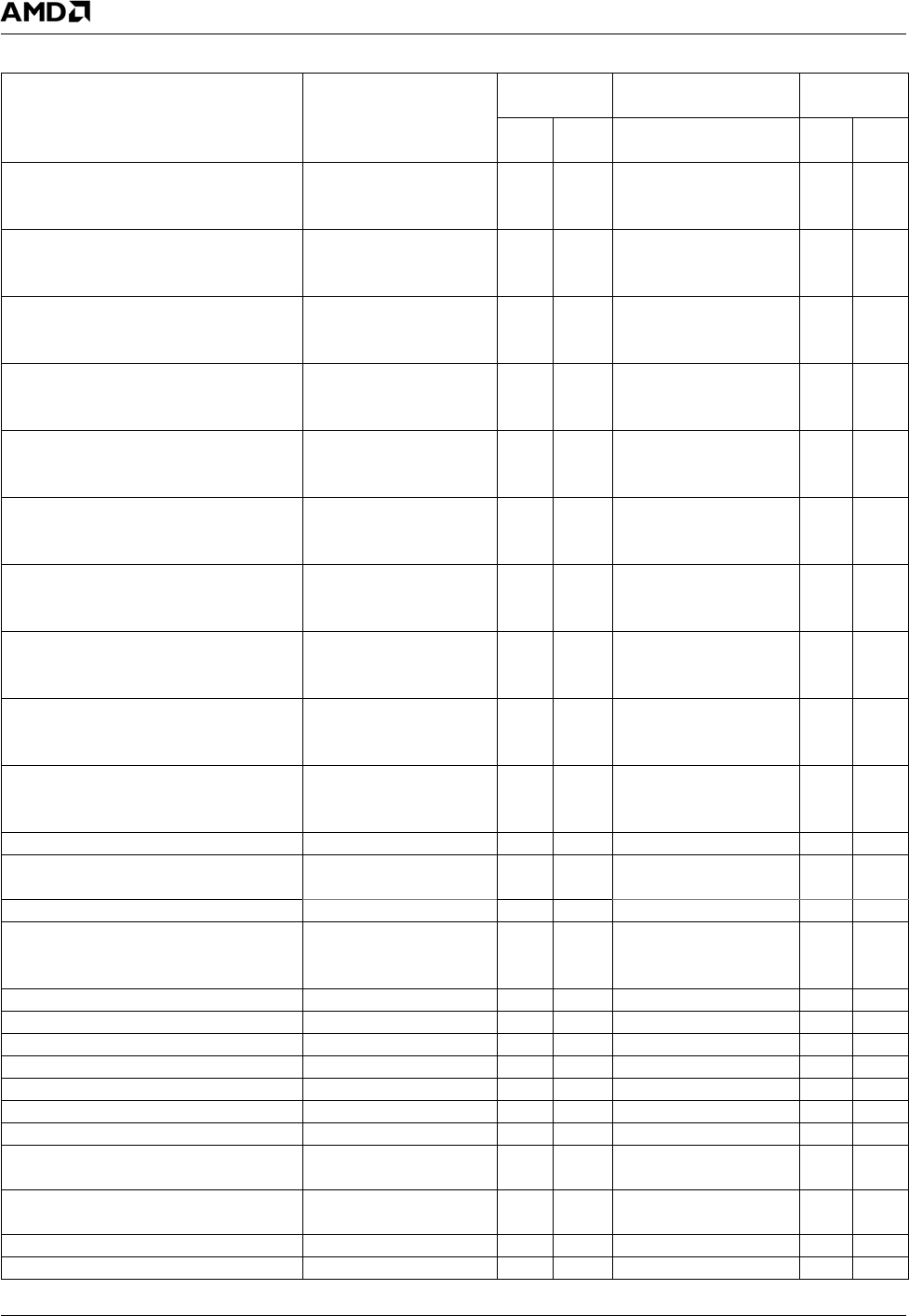

638 AMD Geode™ LX Processors Data Book

Instruction Set

33234H

JNBE/JA Jump on Not Below or Equal/Above -------- r

8-bit Displacement 77 + 1 1

Full Displacement 0F 87 +++ 1 1

JNE/JNZ Jump on Not Equal/Not Zero -------- r

8-bit Displacement 75 + 1 1

Full Displacement 0F 85 +++ 1 1

JNL/JGE Jump on Not Less/Greater or Equal -------- r

8-bit Displacement 7D + 1 1

Full Displacement 0F 8D +++ 1 1

JNLE/JG Jump on Not Less or Equal/Greater -------- r

8-bit Displacement 7F + 1 1

Full Displacement 0F 8F +++ 1 1

JNO Jump on Not Overflow -------- r

8-bit Displacement 71 + 1 1

Full Displacement 0F 81 +++ 1 1

JNP/JPO Jump on Not Parity/Parity Odd -------- r

8-bit Displacement 7B + 1 1

Full Displacement 0F 8B +++ 1 1

JNS Jump on Not Sign -------- r

8-bit Displacement 79 + 1 1

Full Displacement 0F 89 +++ 1 1

JO Jump on Overflow -------- r

8-bit Displacement 70 + 1 1

Full Displacement 0F 80 +++ 1 1

JP/JPE Jump on Parity/Parity Even -------- r

8-bit Displacement 7A + 1 1

Full Displacement 0F 8A +++ 1 1

JS Jump on Sign -------- r

8-bit Displacement 78 + 1 1

Full Displacement 0F 88 +++ 1 1

LAHF Load AH with Flags 9F 2 2 ---------

LAR Load Access Rights 0F 02 [mod reg r/m] -----x--- a g,h,j,p

From Register/Memory 9

LDS Load Pointer to DS C5 [mod reg r/m] 4 9/15 --------- b h,i,j

LEA Load Effective Address ---------

No Index Register 8D [mod reg r/m] 1 1

With Index Register 1 1

LEAVE 22

LES Load Pointer to ES C4 [mod reg r/m] 4 9/15 --------- b h,i,j

LFENCE 11

LFS Load Pointer to FS 0F B4 [mod reg r/m] 4 9/15 --------- b h,i,j

LGDT Load GDT Register 0F 01 [mod 010 r/m] 8-9 8-9 --------- b,c h,l

LGS Load Pointer to GS 0F B5 [mod reg r/m] 4 9/15 --------- b h,i,j

LIDT Load IDT Register 0F 01 [mod 011 r/m] 8-9 8-9 --------- b,c h,l

LLDT Load LDT Register 0F 00 [mod 010 r/m] --------- a g,h,j,l

From Register/Memory 8

LMSW

Load Machine Status Word ---------

From Register/Memory 0F 01 [mod 110 r/m] 8 8 b,c h,l

LODS Load String A [110 w] 2 2 --------- b h

LOOP Offset Loop/No Loop E2 + 2 2 --------- r

Table 8-26. Processor Core Instruction Set (Continued)

Instruction Opcode

Clock Count

(Reg/Cache Hit) Flags

Notes

Real

Mode

Prot’d

Mode

ODI TSZ APC

FFFFFFFFF

Real

Mode

Prot’d

Mode