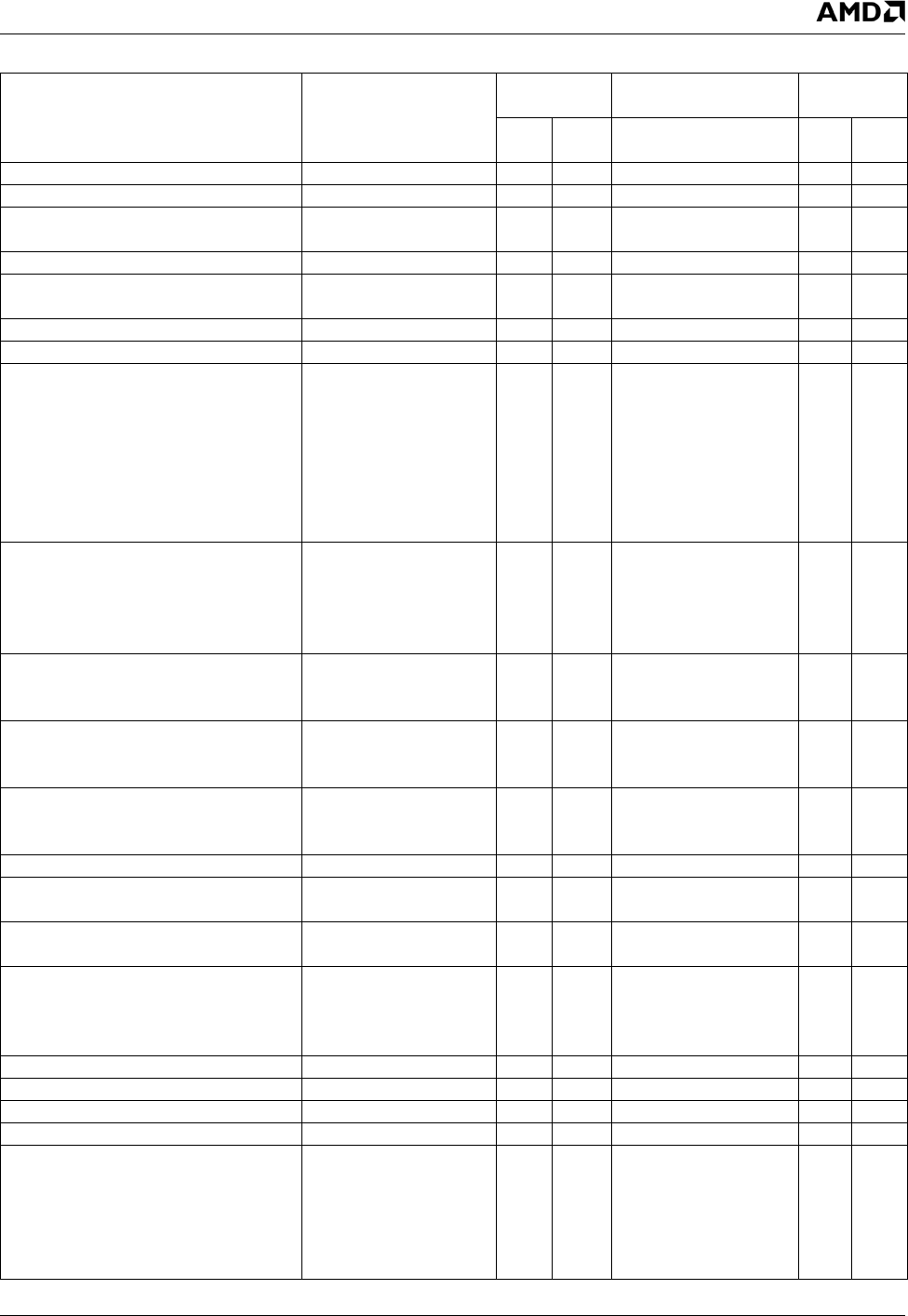

AMD Geode™ LX Processors Data Book 639

Instruction Set

33234H

LOOPNZ/LOOPNE Offset E0 + 2 2 --------- r

LOOPZ/LOOPE Offset E1 + 2 2 --------- r

LSL Load Segment Limit -----x---

From Register/Memory 0F 03 [mod reg r/m] 9 a g,h,j,p

LSS Load Pointer to SS 0F B2 [mod reg r/m] 4 9/15 --------- a h,i,j

LTR Load Task Register ---------

From Register/Memory 0F 00 [mod 011 r/m] 9 a g,h,j,l

LEAVE Leave Current Stack Frame C9 2 2 --------- b h

MFENCE 1

MOV Move Data --------- b h

Register to Register 8 [10dw] [11 reg r/m] 1 1

Register to Memory 8 [100w] [mod reg r/m] 1 1

Register/Memory to Register 8 [101w] [mod reg r/m] 1 1

Immediate to Register/Memory C [011w] [mod 000 r/m] ### 1 1

Immediate to Register (short form) B [w reg] ### 1 1

Memory to Accumulator (short form) A [000w] +++ 1 1

Accumulator to Memory (short form) A [001w] +++ 1 1

MOV Move to/from Segment Registers --------- i,j

To Stack Segment 7/13

To all other segments:

Register/Memory to Segment Register 8E [mod sreg3 r/m] 1 6/13

Segment Register to Register/Memory 8C [mod sreg3 r/m] 1 6/13

MOV Move to/from Control Registers --------- l

Register to CR 0F 22 [11 eee reg] 9-13 9-13

CR to Register 0F 20 [11 eee reg] 2-5 2-5

MOV Move To/From Debug Registers --------- l

Register to DR 0F 23 [11 eee reg] 10/18 10/18

DR to Register 0F 21 [11 eee reg] 8/18 8/18

MOV Move To/From Test Registers --------- ul,u

Register to TR 0F 26 [11 eee reg] 2 2

TR to Register 0F 24 [11 eee reg] 1 1

MOVS Move String A [010w] 4 4 --------- b h

MOVSX Move with Sign Extension --------- b h

Register from Register/Memory 0F B[111w] [mod reg r/m] 1 1

MOVZX Move with Zero Extension --------- b h

Register from Register/Memory 0F B[011w] [mod reg r/m] 1 1

MUL Unsigned Multiply x---xxuux b h

Accumulator with Register/Memory

Multiplier: Byte

Word

Doubleword

F [011w] [mod 100 r/m]

3

4

7

3

4

7

NEG Negate Integer F [011w] [mod 011 r/m] 1 1 x- --xxxxx b h

NOP No Operation 90 1 1 ---------

NOT Boolean Complement F [011w] [mod 010 r/m] 1 1 --------- b h

OIO

Official Invalid Opcode 0F FF 1 8-125 --x0-----

OR Boolean OR 0---xxux0 b h

Register to Register 0 [10dw] [11 reg r/m] 1 1

Register to Memory 0 [100w] [mod reg r/m] 1 1

Memory to Register 0 [101w] [mod reg r/m] 1 1

Immediate to Register/Memory 8 [00sw] [mod 001 r/m] ### 1 1

Immediate to Accumulator 0 [110w] ### 1 1

Table 8-26. Processor Core Instruction Set (Continued)

Instruction Opcode

Clock Count

(Reg/Cache Hit) Flags

Notes

Real

Mode

Prot’d

Mode

ODI TSZ APC

FFFFFFFFF

Real

Mode

Prot’d

Mode